Microchip Technology Inc

Avtor: Gregor Sunderdiek

2017_255_11

Od jedra neodvisne periferne naprave (Core Independent Peripherals, CIP) so avtonomne, medsebojno povezane in inteligentne periferne enote. CIP za izvajanje nalog ne potrebuje storitev centralne procesne enote (CPE) mikrokontrolerja, kar aplikaciji prinaša številne prednosti.

Prvič, za komunikacijo med posameznimi perifernimi enotami CPE ni potrebna. Jedro lahko spi in programskega toka ni treba prekiniti. Logično je, da bo poraba energije za delovanje nižja, če se mikrokontroler nahaja v enem izmed načinov mirovanja in delovanje programske opreme ni potrebno. Centralna procesna enota je tisti del mikrokontrolerja, ki ima največjo porabo toka, zato je razumljivo, da z uporabo CIP porabo energije zmanjšamo.

Druga prednost je, da CIP ne povzročajo prekinitev, kar omogoča veliko hitrejšo komunikacijo. Če jedro CPE izvaja neke procese, določene z izvajanjem programske opreme in morajo to izvajanje periferne enote prekiniti, da bi dosegli določeno dejanje, je za to potrebno veliko časa. Za prekinitev in skok na prekinitveno rutino so potrebni trije cikli, zraven pa še dva cikla za relativni skok in potem še različno število ciklov za preklop konteksta s shranjevanjem podatkov iz registrov na sklad, odvisno od aplikacije. CIP-ji omogočajo, da je komunikacija veliko hitrejša, kot če bi bilo treba delovanje procesnega jedra prekinjati.

Tretjič, uporaba CIP pomeni hitrejši čas do trženja izdelka. Potrebno je napisati manj programske opreme, saj je strojna oprema sposobna sama opraviti svojo nalogo. To hkrati zmanjšuje tveganje glede možnosti napak znotraj obsežnejše programske opreme, zato je ta preglednejša in zahteva manj preverjanja ter pridobivanja soglasij glede skladnosti z različnimi predpisi in standardi. Čas razvoja izdelka je zato lahko znatno krajši kot brez uporabe CIP.

V AVR®mikrokontrolerjih (MCU-jih) so vse neodvisne zunanje naprave povezane prek sistema dogodkov. V sistemu dogodkov multiplekser povezuje generator dogodkov in uporabnika dogodka. Obstajajo sinhroni in asinhroni dogodki. Asinhroni dogodki potrebujejo manj kot en cikel, sinhroni dogodki pa potrebujejo dva cikla ure takta.

Mnoge periferne naprave je mogoče priključiti na sistem dogodkov kot CIP. To so lahko na primer časovniki, števci v realnem času, periodični prekinitveni časovniki (PIT), uporabniško nastavljiva logika (CCL), analogni primerjalnik (komparator, AC), analogno-digitalni pretvornik (ADC), univerzalni serijski sinhroni / asinhroni sprejemnik / oddajnik (USART) in vhodno / izhodne periferne naprave za splošne namene (GPIOS).

Uporaba od jedra neodvisne periferije

Zamuda / razgrnitev

Veliko današnjih aplikacij še vedno uporablja gumb kot eno izmed vhodnih enot. Za vsak gumb je potrebna logika ali del programske opreme, ki iz signala, ki ga povzroči tipka ali stikalo med preklapljanjem, dobimo nepopačeni signal. Za AVR mikrokontrolerje je programska oprema za to nalogo (debouncing) preprosta naloga. To je mogoče storiti z zamudami in / ali logiko v programu, a kljub temu, da ta programska oprema ni zapletena, uporablja procesorske vire. Ali je bil gumb pritisnjen ali ne, se lahko preveri bodisi s pregledovanjem stanja na vsakem posameznem vhodu, bodisi prek prekinitve, ki jo povzroči GPIO krmilnik. Oba načina pa potrebujeta čas in zasedata procesorske vire, da lahko opravita celotno nalogo debouncinga na vhodu do konca.

Zakasnitev signala s CCL filtrom

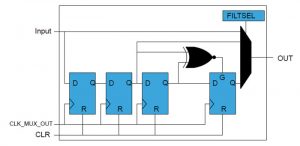

Z uporabo CIP od jedra neodvisne periferije, se debouncing lahko izvede v celoti, brez kakršnegakoli nadzora ali posredovanja centralne procesne enote mikrokontrolerja, torej jedra. Vse, kar je potrebno, je uporabniško nastavljiva logika (Custom Configurable Logic, CCL). GPIO, na katerega je gumb povezan in ki je konfiguriran kot generator asinhronih dogodkov, CCL pa bo eden od uporabnikov sistema dogodkov. Prenos signala bo iz GPIO priključka na vhod CCL brez zakasnitve. Resničnostna tabela v CCL je konfigurirana tako, da je izhod enak vhodu. Izhod iz resničnostne tabele je usmerjen v filter. Takšen CCL filter je prikazan na sliki 1. Iz vhodnega signala je mogoče odstraniti konice signala med preklapljanjem, za izhodni signal pa lahko nastavimo zakasnitev filtra od dveh do petih ciklov (periferne ali katere druge ure). Če uporabljamo počasno uro s frekvenco 32 kHz, tako dobimo zakasnitev signala za 1,5 ms. Mogoče je tudi podaljšati to zakasnitev z drugo uro ali s časovnikom.

Zakasnitev s časovnikom

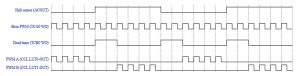

Timer/ Counter B (TCB) je na primer nastavljen na način enkratnega proženja (“Single-Shot”). Kadar časovnik dobi signal dogodka, začne šteti, dokler ne doseže programirane maksimalne vrednosti in se zaustavi. Izhod TCB je povezan naprej na vhod CCL. V CCL lahko prav tako nastavimo želeno kombinacijo zakasnitve signala. Oboje skupaj omogoča zelo prilagodljivo časovno zakasnitev. Vsak nov dogodek v časovniku TCB sproži ponovno štetje od začetka.

Ustvarjanje mrtvih časov

Mrtev čas se uporablja v aplikacijah, kjer so stikala (tranzistor, FET ali IGBT) vezana serijsko med “vročim” napajalnim priključkom in maso (GND). Če sta oba aktivirana istočasno, je vezava kratek stik. Tipičen primer je konfiguracija H-mosta, ki se pogosto uporablja za krmiljenje motorskih pogonov. Odvisno od aplikacije bo mrtev čas bodisi med komutacijami bodisi med posameznimi impulzi pri pulznoširinski modulaciji, (PWM). Mrtvi čas med PWM impulzi je potreben, na primer pri sinusnih pogonih in med komutacijami v 1-polnih brezkrtačnih enosmernih motorjih (BLDC). Mrtvi čas med PWM impulzi lahko ustvari s časovnikom za prikazovanje časovne kode (Time Code Display , TCD).

Za ustvarjanje mrtvih časov med komutacijami potrebujemo dva časovnika, nastavljivo logiko po meri (CCL) in AC (analogni primerjalnik, komparator). Sliki 2 in 3 predstavljata resničnostno tabelo logiko CCL. Timer TCA generira osnovni signal za PWM krmiljenje motorja. AC je zunaj priključen na Hallov senzor za zaznavanje magnetnega polja in je interno prek sistema dogodkov povezan na časovnik TCB. Časovnik TCB generira signal mrtvega časa, če dobi signal iz AC. CCL združuje TCA (PWM), TCB (mrtev čas) in AC signal. Vhodne signale lahko izberete neposredno v konfiguraciji CCL in za to ni potrebna uporaba sistema dogodkov. Med temi moduli se ustvarijo čvrste povezave. CCL nato generira dva PWM signala (glej sliko 4), ki krmili stikala za pogon motorja. Motor teče brez posredovanja CPE. Za več tehničnih informacij poiščite na koncu omenjeni dokument “AVR Application Note AVR42778”.

Samodejni izklop PWM signala

Mnoge aplikacije morajo spremljati porabo toka, tako da ne presegajo najvišje dovoljene ravni. To je mogoče preprosto izvesti z analognim primerjalnikom AC. AC meri napetost (tok skozi upor) prek šuntnega registra. Če tok (padec napetosti) preseže predhodno nastavljeni prag, se mora PWM signal takoj ustaviti. V obeh spodaj opisanih primerih uporabljamo CIP. Izhodni PWM signal se tako lahko ustavi takoj, ko je zaznan prekomerni tok in to brez posredovanja CPE.

Primer LED razsvetljave s TCA in CCL

Časovnik / števec A0 ustvarja PWM signal za krmiljenje svetleče diode (LED). AC se uporablja za zaznavanje prevelikega toka, CCL pa se uporablja za združevanje teh signalov, tako da se PWM samodejno ustavi, če je zaznan previsok tok. AC in TCA0 sta prek sistema dogodkov povezana s CCL. Izhodni signal AC in PWM sta konfigurirana v resničnostni tabeli CCL, kot vidimo na sliki 5. PWM signal se na izhodu pojavi, če se signal za dogodek oblikuje tako, da je AC nič. Če je zaznan prekomerni tok, je AC signal na logični ena in izhod na nič toliko časa, dokler je zaznati previsok tok.

| AC | TCA0 – PWM | OUT |

|---|---|---|

| 0 | 1 | 1 |

| 0 | 0 | 0 |

| 1 | x | 0 |

Slika 5: CCL resničnostna tabela za obravnavanje napake

Primer nadzora motorja s TC

BLDC motor krmili TCD časovnik, ki ustvarja dvo-kanalni PWM signal, poleg tega pa še dva komplementarna kanala PWM signala za krmiljenje štirih metal-oksidnih polprevodniških tranzistorskih stikal (MOSFET) v H-mostu. AC se uporablja za zaznavanje prevelikega toka skozi motor z merilnim uporom s preklopom med motorjem in GND. AC je priključen prek sistema dogodkov s časovnikom / števcem D0 (TCD). Funkcije TCD vključujejo tudi odpravljanje napak. Če je AC prag prekoračen (odkrit prevelik tok), se ta dogodku signalizira TCD in PWM se samodejno zaustavi.

Merjenje časa potovanja signala

Merjenja časa potovanja signala se uporablja za merjenje razdalje, ki jo signal prepotuje. Meritev se začne, ko signal zapusti oddajnik in se ustavi, ko ga sprejemnik zazna. Na podlagi izmerjenega časa in znane hitrosti signala v m/s lahko izračunamo razdaljo. V spodnjem primeru merimo razdaljo z ultrazvočnim signalom. Za to potrebujemo CIP TCA0, TCB0, TCS0, AC in 2x CCL, s katerimi lahko izračunamo čas potovanja signala brez uporabe procesorja.

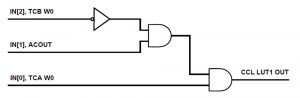

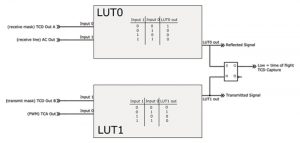

Slika 6 prikazuje vpogledno Tabelo 1 (LUT1), ki ustvarja oddajni signal. TCA Out ustvarja PWM signal in TCD Out B je oddajna maska. Obrnjena oddajna maska in PWM sta logično IN združeni in nato generirata oddajni signal, ki je prikazan z resničnostno tabelo LUT1.

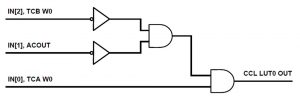

LUT 0 ustvarja odbiti signal. AC Out daje aktivnost na sprejemni liniji, TCD Out A pa je sprejemna maska. Obrnjena maska za sprejem in “sprejemna linija” sta logično IN združeni in ustvarjata odbiti signal, ki je prikazan z resničnostno tabelo LUT0.

Zapah SR je izbrisan (resetiran) s prvim oddanim signalom, obenem pa požene števec v TCD. S signalom od odbitega signala in ob postavljenem izhodu SR zapaha se števec TCD ustavi. Čas potovanja signala je zdaj shranjen kot vrednost v števcu TCD brez uporabe CPE-ja. CPE je potreben samo za izračun razdalje, pri katerem se čas potovanja signala pomnoži s hitrostjo signala. Za več tehničnih informacij v zvezi z ultrazvočnim merjenjem razdalje si lahko ogledate na koncu članka omenjeni dokument “AVR Application Note AVR42779”.

Zaključek

Nova Microchipova serija mikrokontrolerjev iz družine ATtiny1617/1616/1614/817/816/814/417 daje TinyAVR® družini mikrokontrolerjev inovativno in od jedra neodvisno (CIP) periferijo. S CIP periferijo se lahko aplikacija na neke dogodke odzove v realnem času, z manjšo mero potrebnega programskega nadzora in manjšo porabo toka, kot bi bilo to brez njihove uporabe. Ti primeri so pokazali, da je CIP enostavno nastaviti, da je realna učinkovitost takšne rešitve hitrejša in je za takšno rešitev značilna manjšo porabo energije kot za podobne programske rešitve. Celo z zelo zmogljivimi mikrokontrolerji takšne ravni delovanja v realnem času ni mogoče vedno doseči, če pa bi bilo kaj takega to izvedljivo. Bi bila poraba energije nekajkrat višja.

Dodatne informacije o novi družini tinyAVR lahko dobite na spletni strani družine mikrokontrolerjev AVR ATtiny817 na naslovu: http://www.microchip.com/wwwproducts/en/ATTINY817 in v dokumentih:

- AVR42778 “Od jedra neodvisno brezkrtačno krmiljenje DC ventilatorja z uporabo nastavljive logike na ATtiny817” in

- AVR42779 “Od jedra neodvisno ultrazvočno merjenje razdalje z ATtiny817”