Microchip Technology Inc.

Avtor: Robert Perkel

Logika v čipu in prilagodljiva periferna oprema izboljšata aplikacije z zmanjšanjem velikosti kode, manjšo porabo energije in izboljšanjem zmogljivosti sistema z implementacijo diskretne logike in/ali povezovanjem drugih perifernih naprav.

Strojna periferna oprema na čipu je znana po tem, da lahko zmanjša porabo energije, poveča učinkovitost, poveča zmogljivosti naprave in zmanjša velikost kode. Te periferne naprave so na voljo v različnih oblikah, od operacijskih ojačevalnikov in izboljšanih analogno-digitalnih pretvornikov (ADC) do pulznoširinskih modulatorjev (PWM) in univerzalnih časovnikov (UTMR). Ena od najmočnejših vrst teh perifernih naprav so tiste, ki lahko implementirajo diskretno logiko ali povezujejo druge periferne naprave. V tem članku bomo raziskali periferne enote Configurable Logic Cell (CLC), Configurable Custom Logic (CCL), Event System (EVSYS) in Signal Routing (SR) ter kako jih lahko uporabite za povečanje dodane vrednosti vaše zasnove.

CLC / CCL

Periferni napravi Configurable Logic Cell (CLC) in Configurable Custom Logic (CCL) sta programirljivi preglednici LUT (Look-Up Tables), pri čemer je vsaka dejansko enakovredna eni FPGA celici. Logična funkcija, konfigurirana znotraj vsake periferne enote, se določi med izvajanjem. CLC/CCL lahko deluje neodvisno od procesorja, kar omogoča, da v zasnovi nadomesti diskretne logične čipe. Kar zadeva razliko med CLC in CCL; obstajajo manjše izvedbene razlike – CLC je specifičen za PIC® mikrokontroler, CCL pa za AVR® mikrokontroler. Osnovno delovanje vsake periferne enote ostaja enako.

Funkcija debounce za stikala in tipke

Eden najpogostejših primerov uporabe CLC/CCL je izvajanje strojnega razbremenjevanja v povezavi s časovnikom/oscilatorjem. V aplikaciji 2805 (AN2805)[1]so opisani trije načini za izvajanje debounce funkcije z uporabo CLC. Od teh treh sta dve različici CLC dosegli dobro ravnovesje med uporabo strojnih virov in zmogljivostjo. Izvorna koda za vse tri različice je na voljo na portalu Github [2].

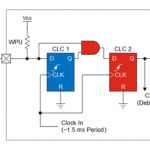

Za izvedbo funkcije debounce je eden od CLC nastavljen kot D-flip-flop za zaklepanje vrednosti iz tipke ali stikala. Drugi CLC logično združi zaklenjeno vrednost iz prejšnje stopnje z neposrednim vhodom in nato zaklene dobljeno vrednost. Takt za oba flip-flopa je nizkofrekvenčni vir ure, ki ga generira časovnik ali oscilator v napravi. Izvedba je prikazana spodaj.

Za CCL v AVR mikrokontrolerjih je to še preprostejše. CCL vsebujejo možnost vhodnega filtriranja, ki učinkovito izvaja isto operacijo dvotaktnega filtriranja, kot je bila izvedena na CLC. Poleg tega lahko CCL-ji dobijo takt iz 1 kHz oscilatorja iz samega mikrokontrolerja. Ta takt je dovolj počasen, da lahko izvede debounce funkcijo.

Dekodiranje enkoderja

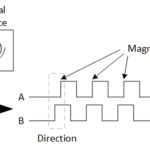

Drugi primer uporabe CLC je izvajanje kvadraturnega dekodiranja. Inkrementalni kvadraturni kodirniki oz. rotacijski enkoderji generirajo dva kvadratna signala, pri katerih ena faza vodi drugo za 90 stopinj. Količina vrtenja je določena s frekvenco signalov, medtem ko faza signala označuje smer vrtenja. Spodnja slika prikazuje primer kvadraturno kodiranega signala.

Za dekodiranje CLC pretvori to obliko signala v dva izhoda, ki predstavljata impulze v smeri urnega kazalca in v nasprotni smeri urnega kazalca. Dva časovnika v mikrokontrolerju štejeta število prejetih impulzov. Ko mora mikrokontroler prepoznati spremembo položaja, se lahko na podlagi štetja vsakega časovnika izvede nekaj preproste matematike, da se določi sprememba od zadnjega odčitka.

Sistem dogodkov

Sistem dogodkov (angl. Event System – EVSYS) je zasnovan tako, da izbere izhodni signal iz druge periferne naprave in ga usmeri v drugo(-e) periferno(-e) napravo(-e) v mikrokontrolerju. To medsebojno povezovanje lahko poteka neodvisno od centralnega procesorja, kar prihrani energijo v načinu spanja ali mirovanja in izboljša zmogljivost. EVSYS je na voljo samo v AVR mikrokontrolerjih.

SR Port

V PIC mikrokontrolerjih je periferna enota, znana kot Signal Routing (SR) Port (priključek za usmerjanje signalov). SR Port je struktura, ki je podobna izhodnim I/O vratom, vendar je zgrajena v notranjosti. S programsko opremo lahko ročno nastavite ali izbrišete bite v notranjosti, tako kot pri standardnem izhodnem I/O registru, podpira pa tudi periferne izhodne signale in funkcionalnost pomičnega (shift) registra.

SR Port priključek dobro deluje tudi s funkcijo izbire perifernih priključkov (PPS), ki jo najdemo tudi v PIC mikrokontrolerjih. PPS razvijalcu omogoča prilagodljivost pri dodeljevanju vhodno-izhodnih signalov, saj omogoča premikanje digitalnih vhodno-izhodnih signalov na različne priključke mikrokontrolerja. Podobno funkcija PPS perifernim napravam omogoča, da posamezno izberejo SR Port „priključke“ kot vhode. To omogoča izdelavo in krmiljenje naprednih strojev stanja (angl. state machines) z uporabo te periferne naprave.

Izbira signala na vezju

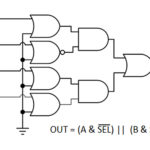

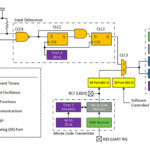

Eden od možnih primerov uporabe SR in CLC vrat je izvedba notranjega multiplekserja za izbiro signalov. Ta se lahko uporablja za notranje samopreizkušanje ali za izbiro enega od N signalov za obdelavo. Za izvedbo tega se CLC uporablja za ustvarjanje multiplekserja 2:1. Možen je tudi multiplekser 4:1, vendar se pri tem uporabijo trije CLC in dva bita iz SR vrat. Za krmiljenje multiplekserja se bit iz SR vrat uporablja kot izbirna linija. Logična izvedba je prikazana spodaj.

Prednost te izvedbe pred PPS je v hitrosti in prilagodljivosti. PPS je mogoče zakleniti in tako preprečiti nenamerne spremembe med izvajanjem. Poleg tega je mogoče nastaviti konfiguracijski bit, ki zagotavlja, da je PPS mogoče odkleniti samo enkrat. Namesto tega nastavitev CLC multiplekserja omogoča, da program spreminja vhode, ne da bi vsakič šel skozi zaporedje odklepanja. Ta primer uporabe je uporabljen v predstavitvenem programu Morsejeve abecede [3] za družino PIC18F56Q71 podjetja Microchip [4]. Demonstracija ustvari preprost oddajnik in sprejemnik Morsejeve abecede – multiplekser se uporablja za izbiro med izhodom oddajnika in zunanjim vhodnim signalom za sprejem.

Znotraj programa so za berljivost definirani enobitni makroji set/clear/toggle za SR Port priključke.

//Select input to decoder

#define SELECT_TX_DECODE() do { RW0_SetLow(); } while(0)

#define SELECT_USER_DECODE() do { RW0_SetHigh(); } while(0)

#define SWITCH_DECODE_SOURCE() do { RW0_Toggle(); } while(0)

Spodnji del kode je odgovoren za čiščenje preklapljanja med vhodnimi viri. Ko sta oddajnik in sprejemnik v mirovanju in je uporabnik na terminal poslal znak ‚#‘, se preklopi vhodni vir.

if (morseTx_isSwitchRequested() &&morseRx_isIdle() &&morseTx_isIdle())

{

//Request to switch input sources

SWITCH_DECODE_SOURCE();

morseTx_clearSwitchRequest();

if (IS_USER_INPUT_ACTIVE())

{

//User Input

printf(„User input is now active.rn“);

}

else

{

//TX Input

printf(„Transmitter input is now active.rn“);

}

}

Izvorna koda tega programa je na voljo na Githubu [5].

Strojno pospešeno izračunavanje paritete

V nekaterih primerih je treba za prenos podatkov ali komunikacijo ustvariti paritetni bit. Izračun paritete v programski opremi je trivialen, vendar počasnejši kot v strojni opremi. Enostavna funkcija je prikazana spodaj.

Opomba: Preskusni vzorec je za te preproste primere shranjen globalno.

boolisOdd_SW(void)

{

boolisOdd = false;

uint8_ttemp;

//Byte Scan

for (uint8_tbyIndex = 0; byIndex<DATA_SCAN_LENGTH; byIndex++)

{

//Bit Scan

temp = data[byIndex];

for (uint8_tbiIndex = 0; biIndex != 8; biIndex++)

{

if (temp&0b1)

{

//Count

isOdd = !isOdd;

}

//Shift bits

temp>>= 1;

}

}

return (isOdd);

}

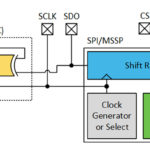

Za pospešitev izračunavanja lahko periferno SPI povezavo uporabljate skupaj s CLC in tako sestavite strojni kalkulator za izračun paritete. Strojna SPI oprema vsebuje zaporedni pomični register za prenos in sprejem podatkov. Izhod strojne SPI opreme (register premika) se lahko pripelje v CLC, da se ustvari kalkulator za izračun paritete, ki deluje bistveno hitreje kot programska različica.

Ta izvedba lahko ponovno uporabi tudi obstoječo periferno SPI enoto, kar še dodatno zniža stroške izvedbe. Za komunikacijo z drugimi SPI napravami je namreč običajno treba potrditi linijo Chip Select (CS). Če pa ni potrjena, se komunikacija ignorira.

Če želite izvesti strojno pospešeno različico, najprej zajemite trenutno zaklenjeno vrednost v CLC. Nato pošljite podatke, ki jih je treba izračunati po pariteti, pri čemer je CS izključen. Nato si oglejte novo vrednost, shranjeno v CLC. Če je nova vrednost enaka prejšnji vrednosti, je bilo prešteto sodo število enic. Če se vrednosti ne ujemata, jih je bilo liho število. Programska oprema za izračun lihe paritete je prikazana spodaj.

boolisOdd_HW(void)

{

boolinitialState = CLC3_OutputStatusGet();

SPI1_BufferWrite(&data[0], DATA_SCAN_LENGTH);

return (!(CLC3_OutputStatusGet() == initialState));

}

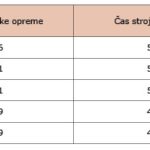

Da bi prikazali prednost hitrosti, je bil na Microchipovi družini PIC16F18146 mikrokontrolerjev [6] zgrajen majhen demo program. Eden od notranjih časovnikov, časovnik 1, se uporablja za štetje števila taktov (FOSC/4), ki so potrebni za izvedbo strojnih in programskih izračunov paritete. Rezultati se za analizo izpišejo na serijski terminal. Kopija rezultatov delovanja pri različnih stopnjah optimizacije prevajalnika je vključena spodaj. Izboljšanje zmogljivosti, prikazano v tem primeru, je odvisno od taktne frekvence mikrokontrolerja in perifernega SPI vmesnika. Izvorna koda tega programa je na voljo na Githubu.

Zaključne misli

Strojna periferna oprema je pomembna značilnost ugnezdenih sistemov. Z njimi lahko mikrokontrolerji postanejo zmogljivejši, učinkovitejši in sposobnejši. Logična in prilagodljiva periferna oprema sta še posebej zmogljivi orodji za izvajanje preprostih nalog, kot sta funkcija debounce ali kvadraturno dekodiranje. Ustvarjalna uporaba strojne periferne opreme izboljša zasnove in premika meje možnosti mikrokontrolerja.

Viri:

1: https://www.microchip.com/en-us/application-notes/an2805

2: https://github.com/microchip-pic-avr-examples/pic18f16q40-clc-switch-debouncing

3: https://github.com/microchip-pic-avr-examples/pic18f56q71-morse-code-mplab-mcc

4: https://www.microchip.com/en-us/products/microcontrollers-and-microprocessors/8-bit-mcus/pic-mcus/pic18-q71

5: https://github.com/microchip-pic-avr-examples/pic18f56q71-morse-code-mplab-mcc

6: https://www.microchip.com/en-us/products/microcontrollers-and-microprocessors/8-bit-mcus/pic-mcus/pic16f18146

Opomba: Ime in logotip Microchip sta registrirani blagovni znamki podjetja Microchip Technology Incorporated v ZDA in drugih državah. Vse druge blagovne znamke, ki so morda tu omenjene, so last njihovih podjetij.