To je privlačen naslov, kaj pa pomeni takšen naslov? Definicija sistema v realnem času je v najpreprostejši obliki tista, ki se izvaja periodično deterministično. Za sisteme v realnem času je determinizem zahteva prvega reda, ker na splošno krmilijo stroje.

Seveda ne želite, da se numerično krmiljeni vrtalni stroj v torek premakne s točke A na točko B v 10 mili-sekundah (ms) in v sredo izvede isto operacijo v 20 ms. Prav tako bi moral sistem za nadzor pilota letala, kadar koli in pod vsemi pogoji, popolnoma natančno nadzorovati letalske površine.

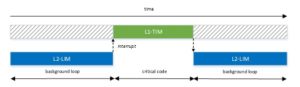

Slika 1 prikazuje deterministični sistem. Periodična prekinitev požara in rutina storitve prekinitve obravnava kritično kodo. Čas izvajanja te kode mora biti determinističen, da ne boste imeli sistema, ki se obnaša, kot je na sliki 2, kjer se posodobitve strojne opreme pojavijo naključno.

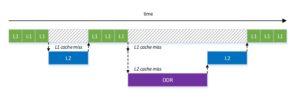

Prav tako je treba bogastvo Linuxa in vse pripadajoče vmesne programske opreme približati strojno nadzorovanim sistemom. Linux potrebuje enoto za upravljanje pomnilnika (MMU) zato, da razvijalcu aplikacije virtualizira fizični pomnilnik. Procesorji, ki ugnezdijo MMU, vključujejo tudi vsaj L1 predpomnilnik in v večini primerov L2 predpomnilnik. Predpomnilniki in determinizem so med seboj pravokotni, kot je prikazano na sliki 3. Tu lahko vidimo, da bodo L1 ali L2 napake povzročile drsenje izvrševanja tako, da bodo zaustavili izvedbeni cevovod, medtem ko bodo vrstice predpomnilnika zapolnjene. Večji predpomnilniki lahko zmanjšajo pogostost zamud predpomnilnika, vendar jih ne odstranijo v celoti.

V procesorjih, ki lahko poganjajo Linux, je dodaten vir drgetanja izvedbe napovednik vej. Procesorska jedra vključujejo napovedovalnik vej za povečanje zmogljivosti na ravni aplikacije. Ne glede na izvedbo so veje predvidene in včasih zgrešene. Ko pride do napake, se vodilo izprazni. Napake vodijo do nedeterminističnega vedenja izvršitve. Med rutino storitve prekinitev (ISR) imajo tabele zgodovine vej, uporabljene v napovedovalniku, zgodovino vej, ki so povezane z zgodovino izvajanja glavne kode aplikacije, ne z zgodovino izvajanja same ISR. To bo povzročilo izpraznjenje vodila znotraj ISR, kar bo povzročilo spremenljiv čas izvedbe od ISR do ISR. Uporaba procesorja, ki uporabniku omogoča onemogočanje napovedovalnika vej, daje razvijalcu aplikacije nadzor nad tem, kje in kako se determinizem uporablja v sistemu. Za širok aplikacijski determinizem lahko napovedovalnike vej popolnoma onemogočite. Seveda so za povečanje zmogljivosti postavljeni napovedovalniki vej, zato bo njihov izklop zmanjšal zmogljivost.

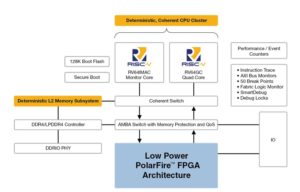

Predstavljamo RISC-V PolarFire SoC FPGA arhitekturo

Obstajajo procesorji, ki lahko zaženejo Linux, vendar ne morejo izvršiti kode deterministično, obstajajo pa procesorji, ki lahko kodo izvajajo deterministično, vendar ne morejo zagnati Linuxa. Ali ne bi bilo lepo, če bi imeli arhitekturo z ugnezdenim kompletom orodij, ki bi lahko podpiral oboje? Nedavno objavljena SoC FPGA arhitektura podjetja Microchip na osnovi RISC-V za PolarFire SoC počne prav to.

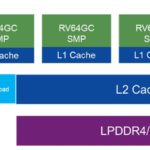

Slika 4 vsebuje štiri 64-bitna RV64GC RISC-V jedra, ki lahko poganjajo Linux, in eno jedro (RV64IMAC), ki ne more zagnati Linuxa. Z drugimi besedami, RV64IMAC ne vsebuje MMU, štiri jedra RV64GC pa vsebujejo MMU. Razlike v naboru navodil med RV64IMAC in RV64GC so preproste; RV64GC vsebuje enoto s plavajočo vejico z dvojno natančnostjo. Za povečanje stopnje determinizma znotraj arhitekture lahko uporabnik izklopi napovedovalnik vej v katerem koli jedru, bodisi po vklopu ali med ISR. Poleg tega so bila za vseh pet jeder izbrana redna vodila, da bi povečali determinizem in se izognili Spectre in Meltdown napadom na jedra, ki ne delujejo.

Do zdaj smo razpravljali le o determinizmu, ki se nanaša na CPU jedra. Kodo je treba izvršiti iz pomnilnika, zato se pogovorimo o pomnilniškem podsistemu v PolarFire SoC. Prvič, ves pomnilniški prostor v PolarFire SoC je skladen. Koherenca je opredeljena s katerim koli pomnilnikom, ki ima več kopij podatkov, tisti upravlja koherence, vsi pomnilniki, ki vsebujejo samo eno kopijo podatkov, pa so po svoji naravi skladni, saj v pomnilniški hierarhiji ne obstajajo nobene druge kopije. PolarFire SoC ima tri pomnilniške podsisteme: L1, L2 in L3. Pomnilniški podsistem L3 vključuje utrjeni 36-bitni krmilnik LPDDR3 / LPDDR4 in DDR3 / DDR4. Dodatni 4 biti so namenjeni dodajanju SECEDED v zunanji pomnilniški podsistem L3.

L1 pomnilniški podsistem

Vsa štiri jedra aplikacije RV64GC imajo vsako svojega 8-smernega asistenta in 32 KB I$TIM. I$ je enak predpomnilniku z navodili in TIM označuje tesno integriran pomnilnik (TIM). I$TIM in D$TIM je mogoče konfigurirati na zahtevo uporabnika, da morata biti vedno en predpomnilnik na boljo za I$TIM in D$TIM. Jedro monitorja RV64IMAC ima 16 KB dvosmernega asociativnega I$TIM in 8 KB DTIM. DTIM je pomnilnik podatkovne beležke, iz katerega je mogoče zagnati kodo. Vse funkcije L1 TIM omogočajo determinističen dostop z nizko zakasnitvijo in omogočajo dvojno zaznavanje napak Singe Error Correct (SECDED).

L2 pomnilniški podsistem

Pomnilniški podsistem L2 je velik 2 MB z možnostjo SECDED in ga je mogoče konfigurirati na tri različne načine. 16-smerni asociativni predpomnilnik, ohlapno integriran pomnilnik (LIM) in pomnilnik beležnice. LIM pomnilnik lahko pripnete na procesor in ga lahko prilagodite v predpomnilnik – z drugimi besedami, LIM-e lahko sestavite v kosih (128KB) in jim dodelite ekskluziven dostop do procesorja. Konfiguriran kot LIM, pomnilniški podsistem L2 zagotavlja deterministični dostop do jedra, na katerega se pripne in je koherenten, saj nobena druga kopija ni v skupni rabi s pomnilniškim podsistemom L1 in L3. LIM je idealen za izvedbo deterministične kode v glavni aplikaciji in ISR-jih. Slika 5 ponazarja deterministični sistem, ko je podsistem pomnilnika L2 konfiguriran kot LIM, L1 pa kot TIM.

Na žalost zaradi napačnega napovedovanja napovedovalnikov vej spremenljivost časa izvajanja ISR še vedno obstaja, tudi če je L2 konfiguriran kot LIM. Slika 6 prikazuje aplikacijo, ki se izvaja, ko je L1 nastavljen kot TIM, L2 pa kot LIM. Vodoravna os označuje prekinitve, navpični dostop pa čas cikla znotraj ISR. Kot lahko vidite, se izvajanje ISR sčasoma spreminja.

Slika 7 nam daje determinizem, ki ga želimo z izklopom napovedovalnikov vej.

Tako kot LIM lahko tudi opombo za beležke konfigurirate v 128 KB (na različne načine) in dodelite CPU jedrom. Scratchpad pomnilnik je idealen kot skupni pomnilniški vir med procesorjem, ki izvaja kodo iz LIM, in procesorji, ki izvajajo kodo iz pomnilniškega podsistema L1 / L2 in L3 (običajno Linux). Če aplikacija RV64IMAC podatke zapiše v beležnico in kopija te lokacije spomina obstaja drugje v pomnilniškem podsistemu L1 / L2 / L3, bo skrbnik koherence zagotovil skladnost. Na ta način lahko aplikacija v realnem času usklajeno deli podatke z aplikacijo, ki se izvaja v uporabniškem Linuxu prostoru.

Slika 8 je ena od možnih konfiguracij mikroprocesorskega podsistema PolarFire SoC. V tej konfiguraciji RV64IMAC deluje v realnem času, medtem ko RV64GC poganja Linux. Če vaša funkcija v realnem času potrebuje delovanje s plavajočo vejico, bi lahko RV64GC služil temu namenu, ker lahko napovedovalnike vej izklopite in podsistem pomnilnika L1 nastavite kot TIM.

Zaključek

Determinizem je ključna zahteva za sisteme v realnem času. Vendar obstaja na trgu veliko procesorjev, ki lahko poganjajo Linux, vendar ne morejo izvajati kode deterministično, in obstajajo drugi, ki lahko kodo izvajajo deterministično, vendar ne morejo zagnati Linuxa. PolarFire SoC ima edinstven, prilagodljiv pomnilniški podsistem, ki omogoča aplikacije, ki se izvajajo v realnem času in Linux aplikacije, da soobstajajo na prilagodljiv, skladen način. Začnite delati s PolarFire SoC na tem naslovu [1].

Vir:

1: https://www.microsemi.com/product-directory/soc-fpgas/5498-polarfire-soc-fpga#getting-started

Avtor: Tim Morin, Direktor strateškega marketinga pri podjetju Microchip

2021-295