Ta je drugi od dveh člankov. V prvem delusmo obravnavali demodulacijo sigma-delta (Σ-Δ) kodiranih podatkov s filtri sinc v aplikaciji za krmiljenje motorja. Pokazali smo pomen sinhronizacije impulznega odziva filtra sinc s pulznoširinsko modulacijo (PWM) in predlagali strategije sinhronizacije; vendar pa so sinhronizacijske sheme otežile iskanje pravilne konfiguracije sistema.

V drugem delu bomo predstavili novo strukturo filtra sinc, ki je optimizirana za sinhronizacijo. Ta filter izboljša zmogljivost merjenja v aplikacijah, ki zahtevajo natančno časovno uskladitev verige za povratno informacijo. Potem bomo govorili o izvedbi filtrov sinc s kodo HDL in optimizaciji filtrov za izvedbo z napravami FPGA. Na koncu bomo predstavili meritev, izvedeno na 3-faznem servopogonu, ki temelji na napravi FPGA.

Filtri sinc, optimizirani za sinhronizacijo

Kot smo že govorili v delu 1, je mogoče s pravilno uskladitvijo impulznega odziva z modulacijo PWM doseči meritve sigma-delta brez napak zaradi zrcaljenja signala. Metoda je sicer jasna, vendar pa je težko (včasih tudi nemogoče) najti konfiguracijo sistema, ki zagotavlja želeni rezultat. To pokažimo na primeru filtra sinc in bloka PWM, ki imata skupno sistemsko uro, ki deluje s frekvenco fsys. Uro modulatorja, fmclk, potem določa enačba 1.1

Tukaj Dmclk pomeni delilnik ure za uro modulatorja, Frekvenco PWM, fpwm, potem določa enačba 2.

DPWM tu pomeni delilnik ure, ki določa frekvenco PWM. Na koncu dobimo z enačbo 3 še stopnjo decimacije (podatkovno hitrost) za filter sinc.

Tukaj Ddec pomeni delilnik ure za decimirano uro. Zaradi preprečevanja lezenja impulznega odziva glede na cikel PWM mora imeti vsak cikel PWM celo število decimacijskih ciklov:

N je celo število. Če kombiniramo enačbi 2, 3 in 4, dobimo:

Očitno lahko enačbo 5 rešimo le z omejenim naborom delilnikov ure Dx. Poleg tega je izbiranje delilnikov ure pogosto strogo omejeno. Sistem mora pogosto delovati z določeno frekvenco PWM (na primer 10 kHz) ali uporabljati točno določeno uro modulatorja (na primer 20 MHz). Druga težava so omejene možnosti pri izbiranju ure modulatorja. Če fsys na primer znaša 100 MHz, je edina razumna izbira za Dmclk zelo omejeno območje celih števil od 5 do 10 (od 20 MHz navzdol do 10 MHz).

Pri vseh teh omejitvah je lahko zelo težko (če ne povsem nemogoče) najti delilnike ure, ki nam ustrezno uskladijo impulzni odziv in PWM. Običajno je potem uporabnik prisiljen izbrati delilnike ure, ki zadovoljijo enačbo 5, namesto da bi izbral delilnike ure, ki zagotovijo želeno frekvenco PWM, uro modulatorja in razmerje signal/šum (SNR). Dodatna težava je, da lahko spreminjanje frekvence s časom povsem onemogoči določitev veljavne konfiguracije. To je pogosto v večosnih sistemih, kjer en krmilnik premikanja sinhronizira več krmilnikov motorjev v omrežju.

Uskladitev sicer omogoča vrhunsko zmogljivost merjenja, vendar včasih ni izvedljiva. V nadaljevanju bomo zato predstavili novo vrsto filtra sinc. Ta filter zagotavlja optimalno zmogljivost merjenja, hkrati pa uporabniku omogoča, da neodvisno izbere vse delilnike ure.

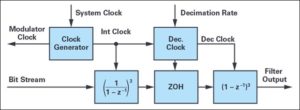

Filter sinc z brisanjem

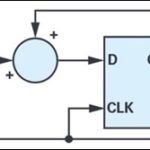

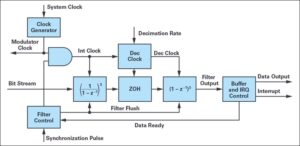

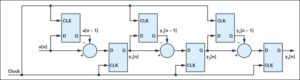

Tradicionalni filter sinc tretjega reda kaže slika 1. Filter tvori uro modulatorja za A/D-pretvornik z deljenjem sistemske ure, A/D-pretvornik pa v filter pošilja 1-bitni podatkovni tok. Filter je sestavljen iz treh kaskadnih integratorjev, 1/(1-z–1), z enako uro kot modulator in treh kaskadnih diferenciatorjev, 1-z–1, ki delujejo z decimirano uro.

Filter sinc in A/D-pretvornik delujeta s stalnim dovodom ure v oba elementa. Posledično dobimo na izhodu filtra neprekinjen tok podatkov s fiksno hitrostjo, ki jo določa decimirana ura. Hitrost podatkov iz filtra je običajno večja od hitrosti posodabljanja krmilnega algoritma motorja, tako da zavržemo veliko izhodnih podatkov filtra. Izhodna vrednost se zajame in uporabi kot povratna informacija samo, ko je središče impulznega odziva poravnano z idealno meritvijo.

Pri modulaciji s prostorskim vektorjem ima fazni tok povprečno vrednost le dvakrat na periodo PWM. Skladno s tem lahko dobimo le dva izhodna podatka brez napak zaradi zrcaljenja na cikel PWM, zato ni potrebe, da bi filter deloval neprekinjeno. V resnici zadošča, da meritev omogočimo samo takrat, ko potrebujemo povratno informacijo, sicer pa jo onemogočimo. Povedano drugače: Meritev deluje le občasno, ko je potrebna, podobno kot pri klasičnem A/D-pretvorniku.

Težava z občasnim delovanjem je, da se uri modulatorja in filtra pridobita iz iste sistemske ure. To pomeni, da zato občasno delujeta tako filter kot tudi A/D-pretvornik, kar ni priporočljivo,saj se zato poslabša zmogljivost. Razlog za to je, da je modulator A/D-pretvornika sistem višjega reda, ki ima določene čase umirjanja in svoje dušenje. Zaradi tega se mora ob prvem vklopu ure za A/D-pretvornik modulator najprej umiriti, da lahko zaupamo izhodnemu podatkovnemu toku. Zaradi reševanja teh težav predlagamo novo strukturo filtra (glejte sliko 2).

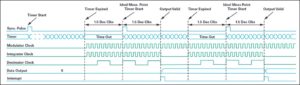

Enako kot pri standardnem filtru sinc ima jedro tri kaskadne integratorje in tri kaskadne diferenciatorje. Vendar pa ima ta filter več dodatnih značilnosti, ki omogočajo nove načine delovanja. Prva je nova funkcija generatorja ure, ki uro modulatorja loči od ure integratorja. To omogoča neprekinjeno dovajanje ure v A/D-pretvornik, ura integratorja pa deluje le, ko želimo dobiti rezultat meritve. Druga novost je nova funkcija za krmiljenje filtra. Krmilni blok glede na sinhronizacijski impulz upravlja vse potrebne časovne uskladitve in proženje, ki so potrebni za delovanje filtra. Glavna naloga krmilnika filtra je brisanje podatkov filtra, ki vključuje inicializacijo vseh stanj in časovnikov filtra pred začetkom nove meritve, ter omogočanje/onemogočanje ure integratorja v pravih trenutkih. Filter ima na koncu še novo enoto z medpomnilnikom in za krmiljenje prekinitev, ki razvršča izhodne podatke ter izbere pravo meritev. Enota z medpomnilnikom in za krmiljenje prekinitev prav tako obvesti aplikacijo za krmiljenje motorja, ko je na voljo nova meritev. Diagram časovne uskladitve na sliki 3 kaže delovanje filtra.

Za začetek meritve se v krmilnik filtra dovede sinhronizacijski impulz. Ta impulz običajno označuje začetek novega cikla PWM. Sinhronizacijski impulz zažene časovnik, ki je nastavljen tako, da se sproži točno1,5 cikla decimacije pred želeno točko merjenja. Takrat se omogočita ura integratorja in decimirana ura ter se začne postopek filtriranja. Po treh ciklih decimacije (čas umirjanja pri filtru sinc tretjega reda) medpomnilnik in krmilnik za prekinitve zajameta izhodni podatek ter sprožita prekinitev. Na sliki 3 vidimo, kako je meritev postavljena na sredino okoli sinhronizacijskega impulza. Zaporedje se ponovi pri naslednjem sinhronizacijskem impulzu, vendar pa po zagonu filtra ura modulatorja ostane vklopljena.

Predlagani filter sinc reši težave s sinhronizacijo klasičnih filtrov sinc. Filter in njegov način delovanja delujeta brez privzemanja frekvence PWM, ure modulatorja ali stopnje decimacije. Enako dobro deluje z vsemi konfiguracijami sistema in celo pri spreminjanju frekvence PWM. Ker se filter dejansko ponastavi za vsako meritev, nanj prav tako ne vpliva medsebojno lezenje ur.

Izvedba filtra sinc v jeziku HDL

Avtorji so ugotovili, da imajo nekateri javno dostopni primeri filtrov sinc v jeziku HDL pomanjkljivosti, ki negativno vplivajo na zmogljivost filtra ali povzročajo nepričakovano obnašanje. V tem razdelku bomo govorili o težavah pri izvedbi in kako zasnovati kodo HDL za optimalno zmogljivost v napravah FPGA.

Integratorji

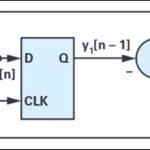

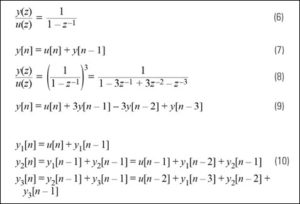

V svoji najčistejši obliki je filter sinc3 sestavljen iz treh kaskadnih integratorjev in treh kaskadnih diferenciatorjev; glejte sliko 1. Najprej poglejmo čisti integrator v z-domeni:2

Pri tem je u vhod in y izhod. Diferenčna enačba integratorja je:

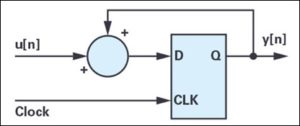

Ta enačba prvega reda je enakovredna akumulatorju, ki je zelo primeren za izvajanje s sinhrono logiko, na primer v napravah FPGA. Tipičen pristop do izvedbe je akumulator s flip-flopom vrste D, ki ga kaže slika 4.

Ta tokokrog lahko v napravi FPGA izvedemo z le nekaj logičnimi vrati. Kadar postavimo tri čiste integratorje v kaskado, ima prenosna funkcija v z-domeni enačbo 8.

Diferenčna enačba za tri kaskadne integratorje je prikazana v enačbi 9:

Poglejmo, kako vhodna vrednost pri vzorcu n vpliva na izhodno vrednost pri vzorcu n.

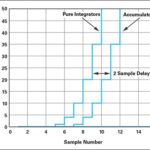

Če so trije integratorji izvedeni kot akumulator s flip-flopom vrste D na sliki 3, dobimo rezultat na sliki 5.

Ker gre za sinhrono vezje z uro, traja več urinih ciklov, da sprememba na vhodu vpliva na izhod. To postane še bolj jasno pri opazovanju diferenčnih enačb za kaskadne akumulatorje (glejte enačbo 10).

Ta diferenčna enačba je povsem drugačna od enačbe za čiste integratorje (glejte enačbo 9). Pri akumulatorjih traja prenos vpliva vhoda na izhod dva urna cikla, pri čistih integratorjih pa vhod takoj vpliva na izhod. To ilustrira slika 6, ki kaže odziv enačbe 9 in 10 na stopnico pri vzorcu številka 5. Kot smo sumili, so akumulatorji v primerjavi z integratorji zakasnjeni za dva urna cikla.

V večini javno dostopnih primerov filtrov sinc je priporočljiva izvedba integratorjev z akumulatorji s flip-flopi vrste D. Glavni argument je majhno število vrat, vendar pa ima tako preprosta izvedba svojo ceno. V primerjavi s skupinsko zakasnitvijo filtra se morda zdi dodatna zakasnitev dveh urnih ciklov modulatorja zanemarljiva, vendar pa zakasnitev vpliva na sposobnost filtra, da oslabi višje frekvence, zato ima taka izvedba akumulatorja manjše efektivno število bitov kot pri čistem integratorju. Poleg tega zahteva predlagani filter z brisanjem za pravilno delovanje idealno prenosno funkcijo. Zaradi tega se pri nobeni izvedbi filtra sinc za izvedbo integratorske stopnje ne zanašajmo na akumulatorje.

Za zagotovitev idealnega odziva sinc3 predlagamo neposredno izvedbo diferenčne enačbe iz enačbe 9. Rezultat kaže slika 7. Vidimo lahko, da blokovni diagram sestavljata dva dela: sinhrona logika (flip-flopi) in kombinatorni del (seštevanje). Taka izvedba zahteva več vrat, vendar pa dosega želeno zmogljivost in zakasnitev filtra.

Diferenciatorji

Podobno kot integratorje mnogi javno dostopni primerih filtrov sinc napačno izvedejo tudi diferenciatorje, kar povzroči slabšo zmogljivost filtra in nepričakovane zakasnitve. V tem razdelku bomo govorili o stopnji diferenciatorja in kako jo izvesti z napravami FPGA za optimalno zmogljivost. Najprej si oglejmo čisti diferenciator v z-domeni v enačbi 11 in nato ustrezno diferenčno enačbo v enačbi 12.2

Za realizacijo diferenciatorja v napravi FPGA najpogosteje uporabimo akumulator s flip-flopom vrste D; glejte sliko 8.

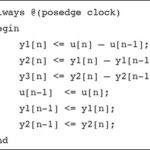

Običajno izvedbo treh diferenciatorjev s flip-flopi vrste D kaže naslednji izsek kode HDL. Tukaj je uporabljen zapis v smislu Veriloga, vendar se enako načelo uporablja tudi drugod.

Kot pri vsaki prireditvi s sinhrono logiko se najprej ovrednotijo vse izjave na desni, nato pa se rezultati prenesejo na levo stran.3. Vse je sinhrono in vse prireditve se posodobijo vzporedno. To povzroča težave, saj izhodne vrednosti (yx[n]) potrebujejo predhodno posodobljene zakasnjene vmesne vrednosti (u[n-1] in yx[n-1]). Tak izsek kode Verilog se zato izvede z logiko, ki jo kaže slika 10.

Sinhrone prireditve pomenijo, da zakasnitev diferenciatorjev namesto pričakovanih treh znaša kar šest urinih ciklov. Ker diferenciatorje poganjamo z decimirano uro, s tem dejansko podvojimo skupinsko zakasnitev in čas umirjanja filtra. Vendar pa to vpliva tudi na slabljenje filtra, ki nima več enakega frekvenčnega odziva kot idealni filter sinc tretjega reda. Na sliki 10 vidimo izvedbo, ki je pogosta v objavljenih primerih filtrov sinc, vendar pa zelo priporočamo, da izberete pristop, ki posnema stopnjo z idealnimi diferenciatorji.

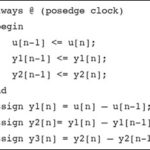

Prejšnji izsek kode Verilog lahko ločimo na dva dela: kombinatorni del, ki izračuna trenutne izhode, in del s sinhrono logiko, ki posodablja zakasnjena stanja. S tako ločitvijo lahko kombinatorni del premaknemo iz sinhronega bloka, kot kaže izsek kode na sliki 11.

Pri kombinatornih prireditvah nimamo dodatnih zakasnitev zaradi izračuna yx, kar skupno zakasnitev s 6 urnih ciklov skrajša na idealne 3 cikle. Slika 12 kaže blokovni diagram priporočene izvedbe diferenciatorjev.

Če kombiniramo predlagani izvedbi kaskadnih integratorjev in diferenciatorjev, dobimo filter sinc z idealnimi lastnostmi glede slabljenja ter zakasnitev. Vse meritve, ki potekajo po načelu sigma-delta, bodo imele koristi zaradi optimizirane izvedbe filtra, še posebej pa filter sinc z brisanjem, ki se zanaša na natančno poznavanje zakasnitve filtra.

Meritve

Predlagani merilni sistem sigma-delta je bil izveden in preizkušen skupaj s krmilnikom servomotorja, ki temelji na sistemu SoC Xilinx® Zynq®-7020.4. Sistem sestavljata 3-fazni servomotor s trajnim magnetom in delovno napetostjo 60 V (Kinco SMH40S5) in 3-fazni stikalni razsmernik z napetostnim virom. V sistemu SoC se izvaja krmilni algoritem motorja z računanjem polja skupaj s programsko opremo za zajemanje izmerjenih podatkov v realnem času.

Za merjenje faznega toka ima sistem dva izolirana A/D-pretvornika sigma-delta (ADuM7701) z dvema filtroma sinc tretjega reda. Filtra sinc sta izvedena po priporočilih v tem članku, vključno z načinom delovanja filtra sinc z brisanjem. Za primerjavo bomo predstavili rezultate meritev za tradicionalni filter z neprekinjenim delovanjem in filter z brisanjem.

Krmilni sistem sicer deluje v zaprtozančnem načinu z računanjem polja, vendar pa vse meritve izvajamo z odprtozančnim krmiljenjem. Zaprtozančna regulacija toka je občutljiva na šum pri merjenju, zato se bo šum sklopil v tokovno zanko. Z odprtozančnim načinom delovanja odpravimo vse učinke tokovne regulacije, kar omogoča neposredno primerjavo rezultatov.

Razen konfiguracije načina in uskladitve z modulacijo PWM so meritve opravljene pri enakih konfiguracijah, kar vključuje stopnjo decimacije, ki je bila nastavljena na 125. Kakršne koli razlike v rezultatih meritev lahko torej pripišemo učinkom pravilne ali nepravilne uskladitve impulznega odziva filtra sinc3 z modulacijo PWM. Krmilni algoritem se izvaja z 10 kHz, ura modulatorja pa je 12,5 MHz.

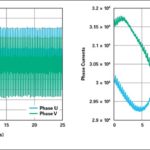

Neusklajen impulzni odziv in neprekinjeno delovanje filtra sinc

V prvem primeru (glejte sliko 13a) impulzni odziv ni povezan z modulacijo PWM. Slika 13b kaže meritve dveh faznih tokov pri ustavljenem motorju, ko jih razsmernik krmili z razmerjem vklopa 50 % na vseh fazah. V tem načinu delovanja vidimo delež šuma v meritvi. Slika 13b kaže fazne tokove, ko motor deluje v odprtozančnem načinu pri 600 vrt/min. Motor ima štiri pare polov, zato znaša električna perioda 25 ms. Oba rezultata kažeta močan šum, ki bi bistveno vplival na delovanje kakršne koli zaprtozančne tokovne regulacije. Raven šuma ni povezana z velikostjo osnovnega faznega toka, zato je šum primerjalno slabši pri manjših obremenitvah. Šum v tem primeru izhaja iz neusklajenega impulznega odziva filtra sinc in nanj povečanje stopnje decimacije (dušenja) filtra sinc ne bi imelo bistvenega vpliva.

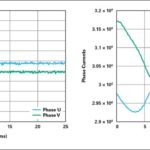

Usklajen impulzni odziv in neprekinjeno delovanje filtra sinc

Slika 14 kaže rezultate meritev pri celem številu ciklov decimacije na periodo PWM in impulznem odzivu, usklajenem z idealno merilno točko. Rezultati na sliki 14 so neposredno primerljivi z rezultati na sliki 13.

Ko sliki 13 in 14 primerjamo, vidimo bistveno manjši šum kljub enaki stopnji decimacije. Primeri ponazarjajo, kako pomembni sta konfiguracija in sinhronizacija sistema, da lahko v celoti izkoristimo zmogljivost signalne verige z A/D-pretvornikom sigma-delta.

Filter sinc z brisanjem

Rezultati z neprekinjenim delovanjem filtra sinc na sliki 14 so zadovoljivi, vendar pa imamo s takim filtrom še vedno težave pri iskanju konfiguracije, ki omogoča sinhronizacijo. Sinhronizacija neprekinjeno delujočega filtra sinc z modulacijo PWM pogosto ni praktično izvedljiva. To težavo rešimo s filtrom sinc z brisanjem.

Slika 15 kaže rezultate meritev za filter sinc z brisanjem. Filter je zasnovan tako, da deluje le 3 cikle decimacije okoli idealne točke merjenja. Zmogljivost je, kot pričakovano, podobna kot pri filtru z neprekinjenim delovanjem na sliki 14.

Filter z brisanjem, uporabljen za primerjavo, ima popolnoma enako konfiguracijo kot filter z neprekinjenim delovanjem. Razlika je v tem, da pri filtru z neprekinjenim delovanjem moramo uporabiti to konfiguracijo, sicer se zmogljivost poslabša, kot kažejo rezultati na sliki 13. Filter z brisanjem pa nasprotno ohrani optimalno zmogljivost s poljubno konfiguracijo sistema.

Raven šuma pri neusklajenem filtru sinc z neprekinjenim delovanjem (slika 13a) znaša približno 120 enot 16-bitnega signala. To pomeni približno 7 bitov izgubljene ločljivosti zaradi šuma. Raven šuma pri filtru sinc z brisanjem (slika 15a) znaša približno 5 enot 16-bitnega signala, kar pomeni manj kot 3 bite izgubljene ločljivosti.

Povzetek

Merjenje faznega toka z A/D-pretvorniki sigma-delta se široko uporablja v krmilnikih motorjev, vendar pa je treba za optimalno zmogljivost pravilno konfigurirati celoten sistem. V tem članku smo govorili o vzrokih za slabo zmogljivost in kako pravilno postaviti sistem.

Konfiguriranje sistema za optimalno zmogljivost povratne informacije o toku je lahko zahtevno in v nekaterih primerih celo nemogoče. Za rešitev te težave smo predstavili novo vrsto filtra sinc. Ta filter deluje samo, kadar je to potrebno, in zagotavlja optimalno zmogljivost s poljubno konfiguracijo sistema.

Izvedba filtra sinc z napravami FPGA zahteva razvoj kode HDL. V članku smo obdelali več možnih tehnik izvedbe, ki zmanjšajo zakasnitve in povečajo slabljenje filtra.

Članek je na koncu predstavil še več rezultatov meritev, ki so pokazali pomembnost sinhronizacije in pa zmogljivosti filtra sinc z brisanjem.

Reference

1 Dara O’Sullivan, Jens Sorensen in Aengus Murray. AN-1265: IsolatedMotor Control Feedback Using the ADSP-CM402F/ADSP-CM403F/ ADSP-CM407F/ADSP-CM408F Sinc Filters and the AD7403. Analog Devices, Inc., april 2015.

2 Alan Oppernheim in Ronald Schafer. Discrete-Time Signal Processing. Tretja izdaja. Prentice Hall Inc., 2010.

3 Rajeev Madhavan. Quick Reference for Verilog HDL. Automata Publishing Company, 1995.

4 Zynq-7000 SoC Data Sheet: Overview. Xilinx, Inc., julij 2018.

5 KNC-SRV-SMH40S Servo. Anaheim Automation, Inc., april 2019.

O avtorju

Jens Sorensen je inženir za sistemske aplikacije pri podjetju Analog Devices, kjer dela na rešitvah za krmiljenje motorjev za industrijsko uporabo. Ima diplomo M.Eng.Sc. iz Univerze Aalborg na Danskem. Zanimajo ga predvsem krmilni algoritmi, močnostna elektronika in krmilni procesorji. Dosegljiv je na naslovu jens.sorensen@analog.com.

O avtorju

Shane O’Meara je inženir za sistemske aplikacije v ekipi za povezano premikanje in robotiko pri podjetju Analog Devices. Njegovo strokovno področje so natančno pretvarjanje in signalne verige za krmiljenje in nadzor v industrijskih aplikacijah za krmiljenje gibanja. Ima diplomo B.Eng. iz Univerze Limerick, v podjetju Analog Devices pa dela od leta 2011. Dosegljiv je na naslovu shane.omeara@analog.com.

O avtorju

Dara O’Sullivan je inženir za sistemske aplikacije v ekipi za povezano premikanje in robotiko v poslovni enoti za avtomatizacijo ter energetiko pri podjetju Analog Devices. Njegovo strokovno področje so pretvarjanje moči, krmiljenje in nadzor v industrijskih aplikacijah za krmiljenje gibanja. Ima diplomo B.E, M.Eng.Sc. in Ph.D. iz univerze University College Cork na Irskem, od leta 2001 pa je delal na številnih aplikacijah za industrijo in obnovljive vire energije na številnih delovnih mestih za raziskave, svetovanje ter industrijo. Dosegljiv je na naslovu dara.osullivan@analog.com.

Avtorji: Jens Sorensen, inženir za sistemske aplikacije, Shane O’Meara, inženir za sistemske aplikacije in Dara O’Sullivan, inženir za sistemske aplikacije

2021-294