Potreba po analogni pripravi signalov, vključno z ADC, še naprej narašča, saj je senzorjev na različnih končnih trgih vedno več.

Microchip Technology Inc.

Avtor: Kevin Tretter

Pričakuje se, da bo celoten trg senzorjev rasel po več kot devetodstotni letni sestavljeni stopnji. Končni trgi vključujejo širitev v okviru različnih IoT aplikacij, avtomatizacije in nadzora tovarn, javnega zdravja in varnosti, zdravstva in avtomobilske industrije. Pri ADC je tržni trend usmerjen v naprave z višjo ločljivostjo in hitrostjo, saj cene takšnih rešitev postajajo dostopnejše.

Kaj je ADC gonilnik (angl. driver)?

Kot pove že ime, so ADC gonilniki posebni ojačevalniki, ki so zasnovani posebej za delovanje skupaj z ADC, vključno z zaporednim približevanjem, zaporednimi in delta-sigma arhitekturami. Ti posebni ojačevalniki so kritične komponente vezja, ki omogočajo delovanje ADC s polno zmogljivostjo, in so postali še pomembnejši z razvojem pretvornikov z višjo hitrostjo in ločljivostjo.

Razumevanje ADC vhodov

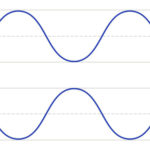

Preden začnemo razpravljati o tehničnih funkcijah, ki jih zahteva ADC gonilnik, je koristen kratek pregled vhodne arhitekture današnjih ADC. Diferencialni signal lahko opredelimo kot dve vozlišči, ki imata enake, vendar nasprotne signale okoli fiksne točke (imenovane raven skupnega voda). Dve signalni vozlišči se običajno imenujeta pozitivno in negativno (ali neinvertirajoče in invertirajoče), kot je prikazano na sliki 1.

V zgornjem primeru je polna vhodna napetost 5 V od vrha do vrha diferencialno, pri čemer vsak signal niha 2,5 V od vrha do vrha. Raven skupnega načina v tem primeru je 2,5 V. Večina današnjih zmogljivejših ADC ima diferencialno vhodno arhitekturo, saj zagotavlja boljšo zmogljivost (v primerjavi z enojnimi vhodi). Te prednosti delovanja vključujejo zmožnost dušenja šuma skupnega načina in skupnih interferenčnih signalov ter povečanje dinamičnega razpona za 6 dB (ali faktor 2).

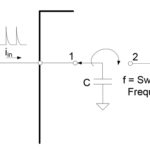

ADC-ji so lahko še posebej težaven izziv za oblikovalce sistemov, saj ponujajo različne vhodne arhitekture vzorčenja, ki jih je treba upoštevati na ravni sistema. V tem članku se bomo osredotočili na ADC-je, ki za vzorčenje vhoda uporabljajo strukturo s preklopnimi kondenzatorji (angl. switched capacitor). V svoji najosnovnejši obliki je ta vhodna struktura sestavljena iz razmeroma majhnega kondenzatorja in analognega stikala, kot je prikazano na sliki 2.

Ko je stikalo v položaju 1, se kondenzator za vzorčenje napolni do napetosti vozlišča za vzorčenje, v tem primeru VS. Stikalo se nato preklopi v položaj 2, kjer se nakopičeni naboj na kondenzatorju za vzorčenje prenese na preostalo vezje za vzorčenje. Postopek se nato začne znova.

Vhod s preklopnim kondenzatorjem brez ojačevalnega vezja, kot je zgoraj opisani, lahko povzroči precejšnje težave na ravni sistema. Tok, ki je potreben za polnjenje kondenzatorja za vzorčenje na ustrezno napetost, je treba zagotoviti iz zunanjega vezja, priključenega na vhod ADC. Ko stikalo kondenzator preklopi na vozlišče za vzorčenje (položaj stikala 1 na sliki 2), je za začetek polnjenja kondenzatorja potreben velik tok. Velikost tega trenutnega toka je odvisna od velikosti kondenzatorja za vzorčenje, od frekvence, pri kateri se kondenzator preklaplja, in od napetosti na vozlišču za vzorčenje. Ta preklopni tok lahko opišemo z naslednjo enačbo:

iin = CVf

kjer je C kapacitivnost kondenzatorja za vzorčenje, V je napetost na vozlišču za vzorčenje (v tem primeru označena kot VS), f pa je frekvenca, pri kateri se stikalo za vzorčenje vklaplja in izklaplja. Ta preklopni tok povzroči visoke tokovne konice na vozlišču vzorčenja, kot je prikazano na sliki 2.

Posledice tega preklopnega toka je treba upoštevati pri načrtovanju analognega vezja pred A/D pretvornikom. Ko vhodni tok prehaja skozi katero koli upornost, se pojavi padec napetosti, kar povzroči napako napetosti na vozlišču vzorčenja A/D pretvornika. Do popačenja lahko pride tudi, če se vhodno vozlišče pred naslednjim ciklom vzorčenja ne ustali v celoti.

Rešitev: ADC gonilniki

Ohranjanje zahtevane celovitosti signala senzorja, da bi lahko v celoti izkoristili prednosti teh ADC z višjo ločljivostjo in hitrostjo, postane zelo zahtevno. S povečevanjem ločljivosti in hitrosti ADC postanejo učinki šuma in popačenj senzorskega signala bolj opazni. Pri višjih hitrostih vzorčenja ADC je treba paziti, da se vhodni signal pred vzorčenjem ustali in da se signali z večjo pasovno širino ne mešajo nazaj v pasovno širino signala, ki nas zanima.

Da bi premagali te izzive pri oblikovanju signalov, je za številne ADC aplikacije potreben ADC gonilnik, ki zagotavlja zadostno poravnavo in preprečevanje mešanja. Kot je opisano zgoraj, ima večina sodobnih ADC diferencialno vhodno arhitekturo. Ena od glavnih funkcij ADC gonilnika je zagotoviti pretvorbo vhodnega signala iz enojnega v diferencialni signal (čeprav lahko prav tako enostavno obdelujejo tudi diferencialni vhodni signal).

Naslednja funkcija ADC gonilnika je ojačenje vhodnega signala, s čimer se preostalo vezje izolira od vnosa naboja na vhodno vozlišče ADC-ja. ADC gonilnik zagotavlja takojšnje polnjenje, da se vozlišče vzorčenja umiri v času sledenja, s čimer se zmanjšajo vsa popačenja, povezana z umirjanjem. Pri postavitvi ADC gonilnika in pretvornika na plošči je treba paziti na minimalno upornost vezi od izhoda gonilnika do vhoda v ADC.

Večina gonilnih ojačevalnikov za ADC-je ima na voljo tudi priključek, s katerim lahko uporabnik nivojsko premakne napetost skupnega načina. Ta funkcija je idealna za zagotavljanje, da je dobljeni diferencialni signal osredotočen znotraj območja vhodne napetosti ADC-ja, s čimer se poveča dinamično območje. Ker se delovne napetosti še naprej znižujejo, je dinamični razpon še bolj pomemben za zagotavljanje polne ločljivosti vhodnega signala.

Podobno kot večina ojačevalnih komponent lahko tudi gonilniki ADC zagotavljajo ojačitev vhodnega signala in aktivno filtriranje. Opozoriti je treba, da ima večina ADC gonilnikov razmeroma majhno ojačenje, običajno le 1 ali 2 V/V. Z nizkim ojačenjem v zaprti zanki ojačevalnika se ojačenje zanke maksimizira, kar ima za posledico najmanjše popačenje. Če ima na primer ojačevalnik ojačenje v odprti zanki 100 dB in je konfiguriran za ojačenje v zaprti zanki 200 ali 46 dB, ostane za zagotavljanje linearnosti le 54 dB rezerve ojačenja v odprti zanki ali približno en del na 500. Zato je običajno, da je ločena stopnja ojačitve nameščena blizu vira signala, da se poveča razmerje med signalom in šumom.

Zaradi širjenja senzorjev na najrazličnejših končnih trgih se je treba dodatno osredotočiti na vezja za oblikovanje signalov. Ker se stroški ADC z visoko ločljivostjo in višjo hitrostjo še naprej znižujejo, je izboljšanje zmogljivosti vse bolj zahtevno.

Če želite kar najbolje izkoristiti svoj pretvornik podatkov, je ADC gonilnik ključnega pomena za optimizacijo zmogljivosti, hkrati pa izvornemu signalu dodaja zanemarljive napake popačenja, šuma in časa poravnave. Posebni čipi, kot je diferencialni gonilnik MCP6D11 [1], so posebej zasnovani za povečanje zmogljivosti hitrih ADC z visoko ločljivostjo.

Vir:

1: https://www.microchip.com/en-us/product/MCP6D11

Opomba: Ime in logotip Microchip sta registrirani blagovni znamki podjetja Microchip Technology Incorporated v ZDA in drugih državah. Vse druge blagovne znamke, ki so morda tu omenjene, so last njihovih podjetij.