Univerza v Ljubljani, Fakulteta za elektrotehniko

Avtor: Izr. prof. dr. Marko Jankovec

V tem prispevku se bomo lotili ene izmed osnovnih tehnik načrtovanja vezij in sicer blokirnih kondenzatorjev, ki poleg stabilizacije napajalne napetosti komponent v vezju močno vplivajo tudi na elektromagnetno skladnost vezja.

Kaj sploh je tehnika blokiranja? V bistvu je to dodajanje enega ali več kondenzatorjev med napajanje in maso k elementom na tiskanem vezju, ki za svoje delovanje potrebujejo visokofrekvenčne napajalne tokove. Vloga teh kondenzatorjev je dvojna:

- Zmanjšujejo površine zank visokofrekvenčnih tokokrogov, ki bi sicer tekli po celotni dolžini poti od napajalnika do komponente in tako neposredno zmanjšujejo tokovno generirane diferencialnemotnje (glej prispevek v SE 342) in

- skrbijo za stabilno napajalno napetost komponent.

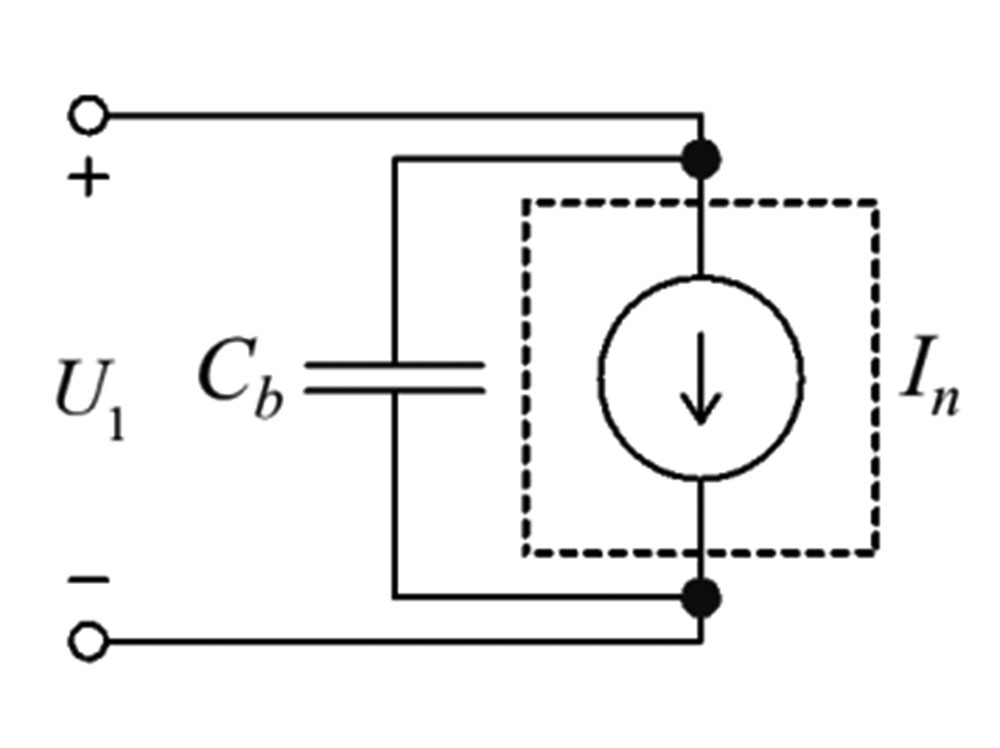

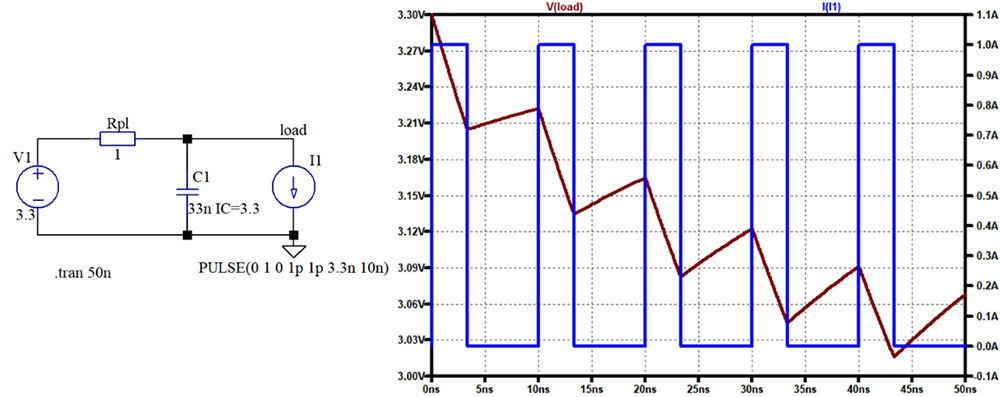

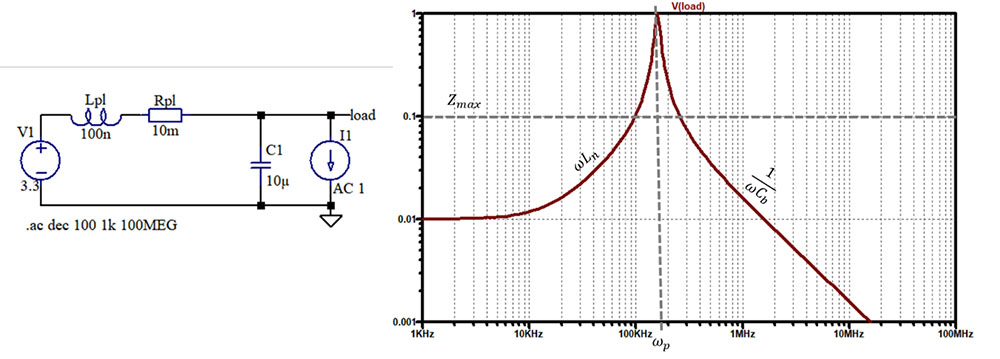

Slika 1 prikazuje osnovni princip delovanja blokirnega kondenzatorja Cb, ki ga postavimo med napajane in maso čim bliže elementu, katerega napajalni tok In je vir motnje.

A najprej se vprašajmo, katere komponente sploh potrebujejo stabilizacijo napajanja in kakšna je narava njihovih napajalnih tokov? Na splošno poznamo pasivne (upori, kondenzatorji, …) in aktivne komponente, ki pa se najdejo v diskretni (diode, tranzistorji) ali integrirani obliki (čipi). Čipe pa najbolj na grobo delimo na analogne in digitalne. Vsa vezja v osnovi za svoje delovanje zahtevajo bolj ali manj stabilno napajalno napetost. Pri analognih vezjih je frekvenčna vsebina napajalnega toka v skladu s signali v vezju, medtem kot je napajalni tok digitalnih vezij posledica preklapljanja množice tranzistorjev, ki sestavljajo logične sklope vezja. Še posebej to velja za digitalne čipe, ki vsebujejo na tisoče, milijone ali celo milijarde majhnih tranzistorjev, kot so FPGA, mikroprocesorji, komunikacijski vmesniki, itd. Njihova frekvenčna vsebina se razteza v širokem frekvenčnem področju, ki presega najvišjo frekvenco morebitne ure digitalnega vezja.

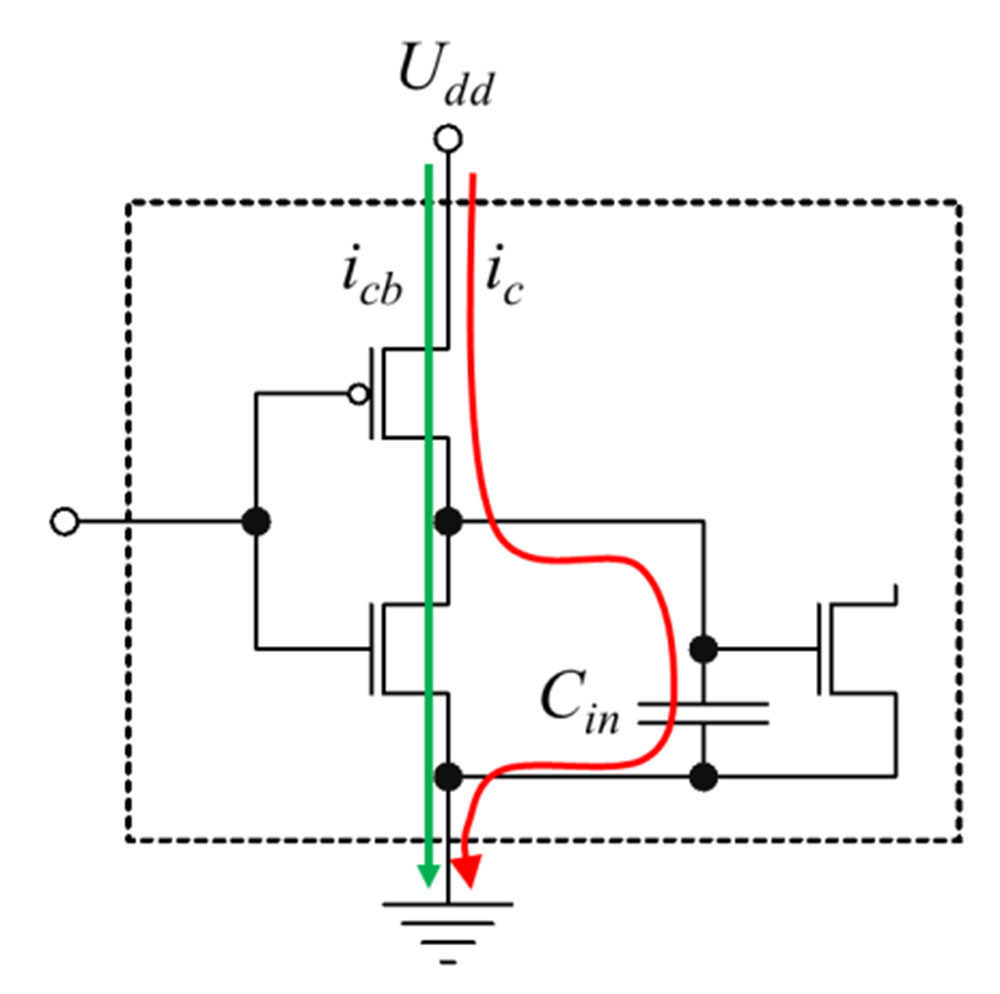

Posamezni tranzistorji ob preklopih polnijo in praznijo kapacitivnosti sosednjih tranzistorjev, kamor so povezani (rdeča puščica na sliki 2). Poleg tega pa lahko v času preklopa steče zelo na kratko tok prek obeh tranzistorjev (zelena puščica na sliki 2.)

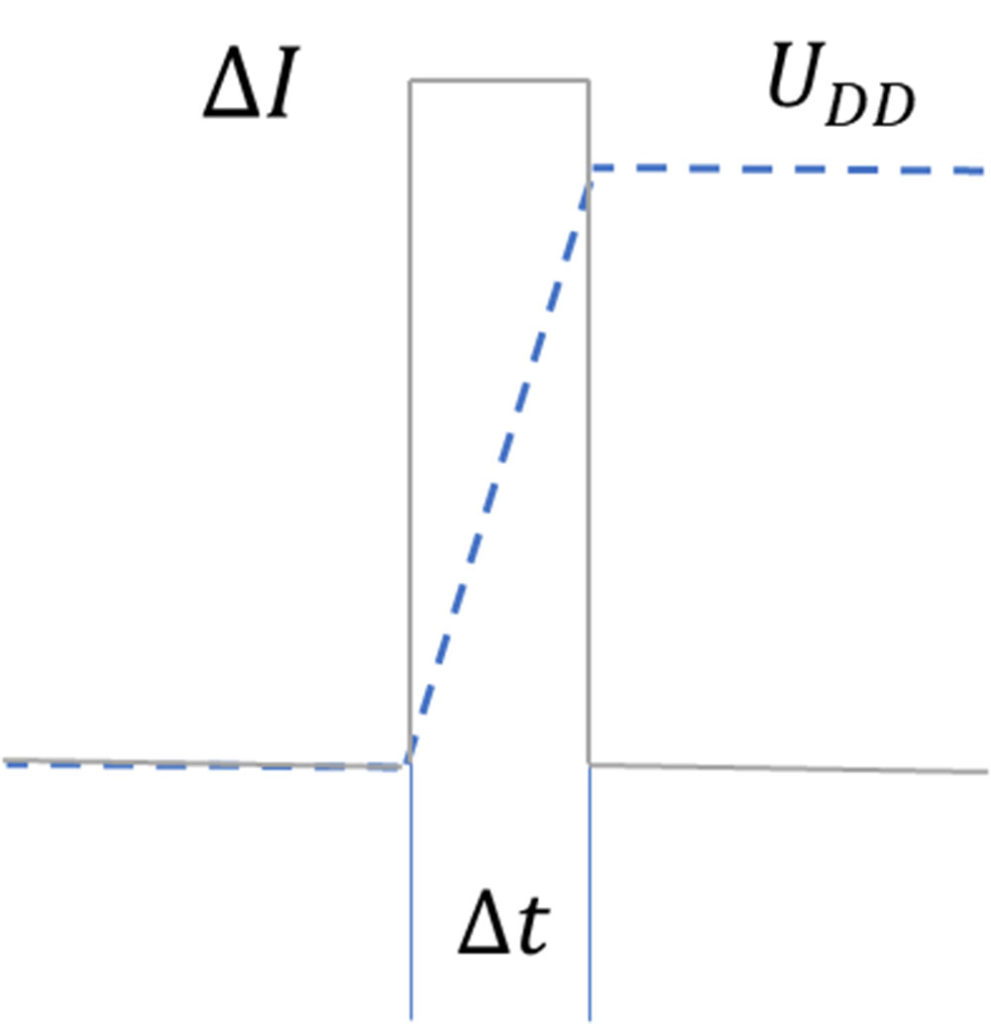

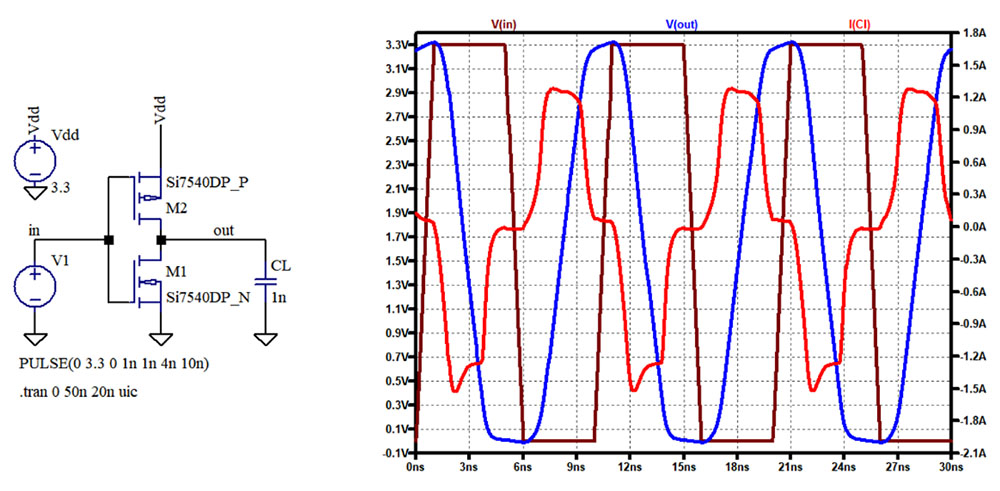

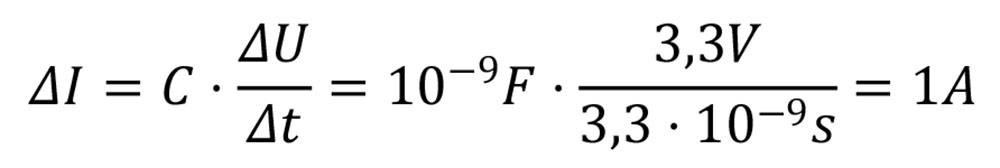

Poglejmo si, kakšne napajalne tokovne sunke lahko sploh pričakujemo. Privzemimo nek fiktivni primer čipa, ki teče na frekvenci 100 MHz na napajalni napetosti 3,3 V in se omejimo zgolj na tok polnjenja kondenzatorjev. V enem samem preklopu, ki npr. traja Δt=3,3ns se mora tako za ΔU=3,3V napolniti na milijone vrat MOSFET-ov s skupno kapacitivnostjo npr. C=1nF, kar nam da tokovne sunke F1.

Pri tem smo naredili nekaj predpostavk, kot npr. ta, da je strmina poteka napetosti na kondenzatorju konstantna znotraj časa Δt, kot kaže slika 3. A podobno nam pokažejo tudi rezultati LTspice simulacije na sliki 4.

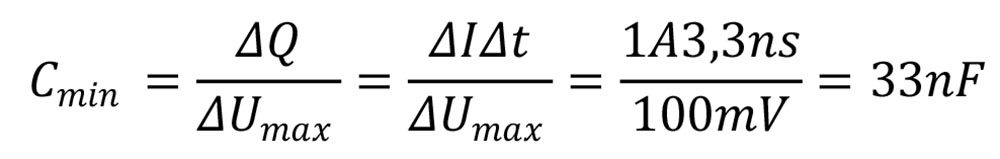

Seveda nas sedaj zanima, kolikšna je minimalna vrednost blokirnega kondenzatorja Cmin, ki bo pri takih tokovnih sunkih lahko zagotavljal stabilno napajanje. Pri tem privzemimo, da kondenzator znotraj časa Δt dovaja s konstantnimi tokovnimi impulzi ΔI ves potreben naboj čipu in da je dovoljen padec napetosti na blokirnem kondenzatorju znotraj enega cikla ΔUmax=100mV, F2.

LT spice simulacija na sliki 5 tega fiktivnega primera kaže podobne rezultate, kjer ob vsakem tokovnem impulzu pade napetost na blokirnem kondenzatorju za približno 100 mV. Vendar pa smo v sami enačbi zanemarili polnjenje kondenzatorja, kar pa smo lahko v sami simulaciji brez težav dodali in sicer se blokirni kondenzator s strani napajalnika polni prek upornosti povezovalne linije, kar se vidi kot povečanje napajalne napetost v času, ko tok ne teče.

Seveda bi si lahko upornost izmislil ravno takšno, da bi se kondenzator vmes med pulzoma ravno napolnil na izhodiščno vrednost in bi bil problem napajalne napetosti rešen, a prav gotovo bi taka rešitev ostala zgolj na teoretični ravni, v praksi pa se niti ne bi obdržala. Kaj se torej dogaja v praksi? V modeliranju našega fiktivnega primera nismo upoštevali impedance vira napajalne napetosti.

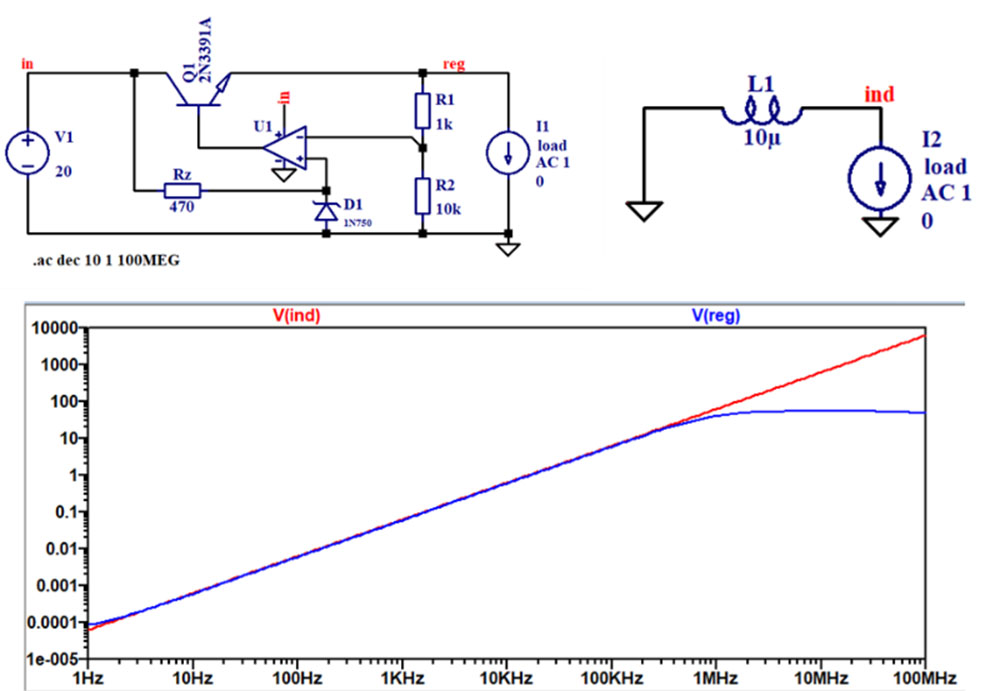

Kakšna pa je pričakovana impedanca napajanja v vezjih? V vezjih za generacijo napajalne napetosti običajno nimamo na voljo kar cele množice raznih baterij, temveč uporabljamo napetostne regulatorje, ki iz enega napajalnega vira generirajo želene napetosti. Vzemimo najbolj enostaven primer napetostnega regulatorja, ki je prikazan na sliki 6 levo. Deluje tako, da napetost izhoda prek povratne vezave primerja z referenco in s tem signalom krmili močnostni tranzistor. Ko se napajalni tok poveča, napetost rahlo pade, kar prek negativne povratne vezave odpre tranzistor. Pri nizkih frekvencah ta povratna vezava deluje dovolj hitro, da uspe stabilizirati izhodno napetost. Ko pa se frekvenca napajalnega toka poveča, pa povratna vezava pa začne fazno zaostajati, kar posledično povzroči povečano izmenično komponento izhodne napetosti. Če pogledamo posledično impedanco, vidimo, da ta s frekvenco raste, kar pomeni, da ima induktivni značaj in se lepo prilega impedanci tuljave z induktivnostjo 10 µH (slika 6 desno).

Napetostni regulatorji v vezjih se torej obnašajo kot zaporedna vezana induktivnost, pri čemer ji dodamo še upornost in induktivnost povezave na tiskanem vezju.

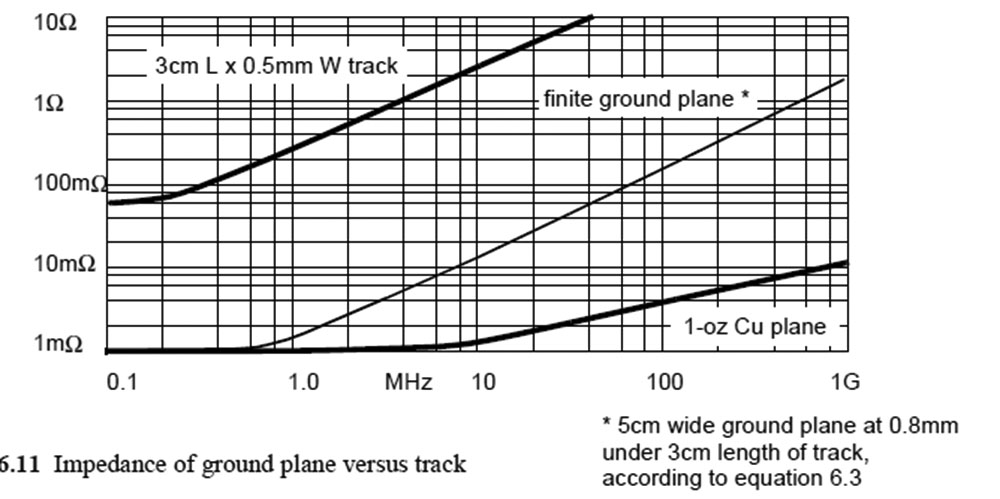

Slika 7 prikazuje potek impedance linije dolžine 3 cm in širine 0,5 mm v primerjavi s 5×5 cm veliko površino mase in neskončno površino mase. Vsi trije primeri kažejo uporovni značaj pri nizkih frekvencah, kjer pa hitro z višanjem frekvence prevlada induktivni značaj. Omenjena linija ustreza vrednosti nekje 6 nH/cm, medtem ko imajo velike površine mase impedanco za več razredov velikosti nižje. Impedanco napajalnih virov v vezjih torej modeliramo kot zaporedno vezane upornost in induktivnost vira in povezave na tiskanem vezju, kot kaže slika 8. Kako pa upoštevati to impedanco napetostnega vira pri dimenzioniranju blokirnega kondenzatorja?

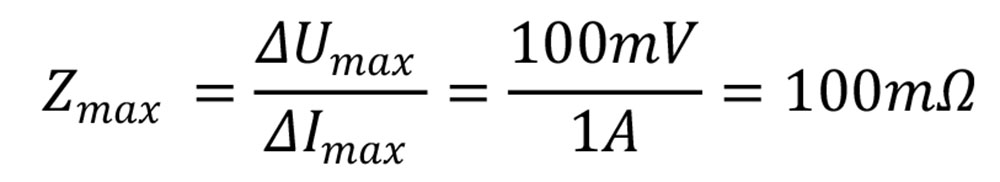

V osnovi želimo zagotoviti impedanco dovolj nizko v dovolj širokem frekvenčnem področju, kar dosežemo z blokirnim kondenzatorjem, kateremu impedanca pada z višanjem frekvence. Kolikšna pa naj bi bila maksimalna impedanca napajalnega vezja, pri katerem bi čip še nemoteno delal? Približno jo lahko določimo tako, da delimo maksimalno dovoljeno nihanje napetost z amplitudo tokovnih sunkov, ki jih v napajanju povzroča čip F3.

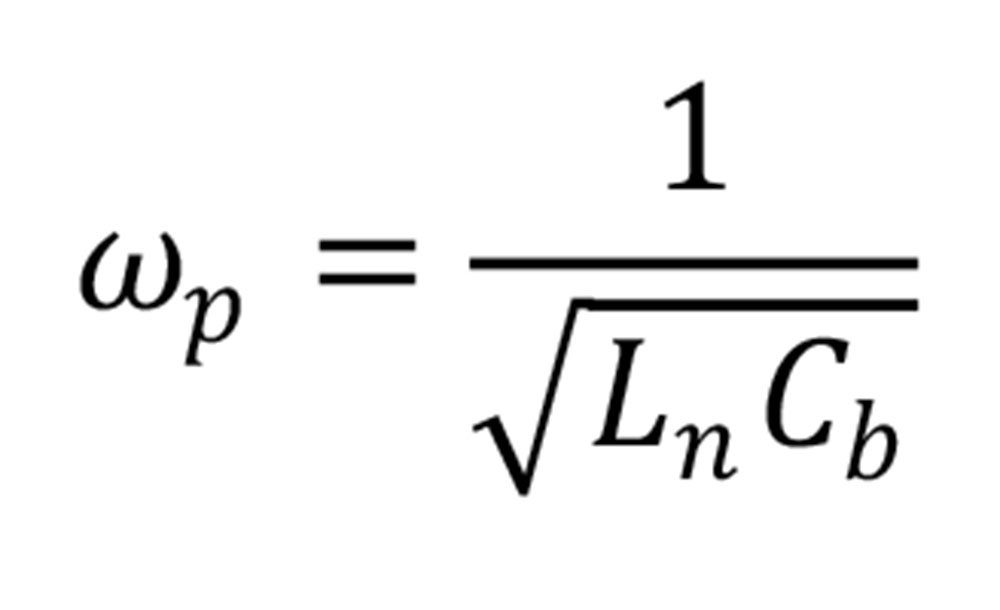

Za konec tega prispevka določimo vrednost blokirnega kondenzatorja z upoštevanjem impedance napajanja. Privzemimo spet fiktivni primer, da imamo idealni napetostni vir in povezavo na tiskanem vezju z induktivnostjo 100 nH in upornostjo 10 mΩ. Taka linija doseže mejo maksimalne impedance že pri frekvenci ωp F4.

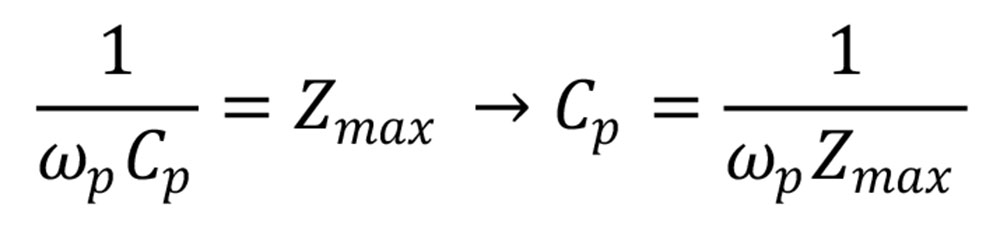

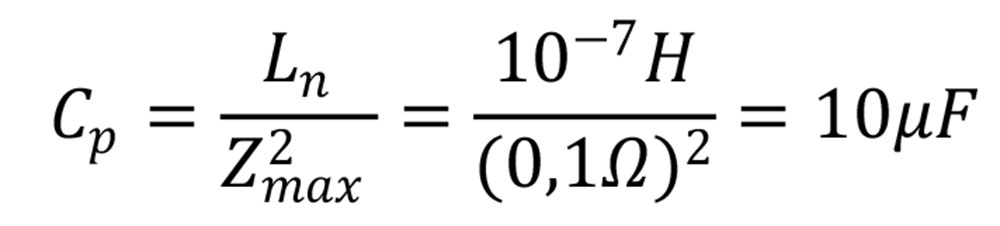

In npr. pri tisti frekvenci si želimo, da bi impedanca blokirnega kondenzatorja že prevladala in jo znižala. Torej izberemo kapacitivnost tako, da bo pri frekvenci ωp impedanca kondenzatorja tudi enaka Zmax F5.

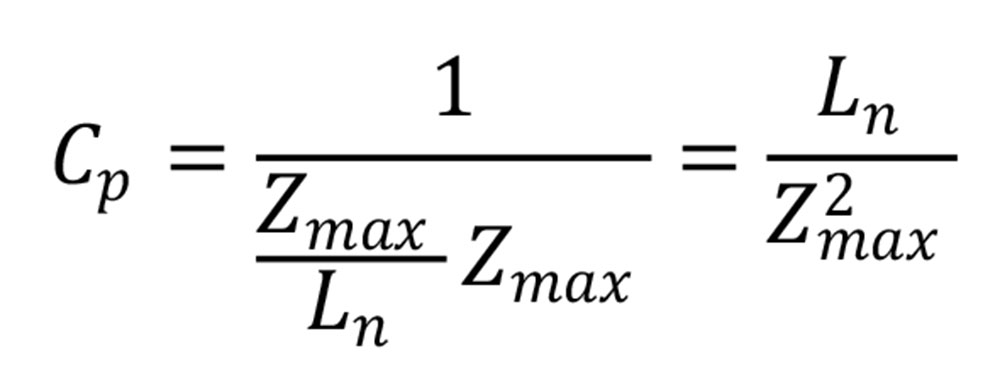

Če obe enačbi združimo, dobimo izraz za kapacitivnost blokirnega kondenzatorja F6.

V našem primeru dobimo F7.

Celoten potek impedance je prikazan na sliki 9. Pri nizkih frekvencah impedanca raste zaradi induktivnega značaja, pri frekvencah nad ωp pa prevlada impedanca blokirnega kondenzatorja. Kako pa se ti dve impedanci seštejeta v resonanci? Tukaj pa je odvisno od kvalitete nihajnega kroga, ki ga sestavljata induktivnost napajalne povezave in kapacitivnost blokirnega kondenzatorja, kajti pri frekvenci ωp imamo ob izbranih vrednostih induktivnosti in kapacitivnosti resonanco paralelnega nihajnega kroga F8.

Kako bi izgledala, si poglejmo kar v LTspice simulaciji na sliki 10. Vidimo, da ob dodatku idealnega blokirnega kondenzatorja vzporedno s induktivnostjo napajanja z zelo nizko serijsko upornostjo nastane kvaliteten paralelni nihajni krog z zelo izrazito paralelno resonanco, ki izdatno presega zadano maksimalno vrednost impedance napajanja.

Kaj to pomeni v praksi in kako se tega problema lotimo, pa v prispevku v naslednji reviji.