Avtor: Klemen Bravhar

Avtomatizacija različnih procesov se že nekaj časa seli iz industrijskega okolja v gospodinjstva, kjer uporabnikom pomaga pri vsakdanjih opravilih, kot so varčevanje z električno energijo, upravljanje razsvetljave, načrtovanje delovanja pametnih gospodinjskih aparatov in številne druge storitve.

Vse te naprave temeljijo na mikrokontrolerjev oziroma procesorjih, integriranih v številne celostne rešitve. Rešitve delujejo po principu »plug-and-play« in omogočajo povezovanje storitvami v oblaku, kot so SpaceLYnk, Simatek, Sintel M221, in mnoge druge.

Ta vsebina je samo za naročnike

Mikrokontrolerji imajo v številnih primerih omejitve glede števila vhodno-izhodnih signalov ter njihove funkcionalnosti. Za povečanje fleksibilnosti in razširjenosti integriranih sistemov lahko izkoristimo prednosti programabilnih logičnih vezij (Field Programmable Gate Array – FPGA). Gre za polprevodniške komponente, ki jih je mogoče po izdelavi programsko konfigurirati za izvajanje različnih digitalnih logičnih nalog. Sestavljene so iz mreže nastavljivih logičnih funkcijskih blokov, ki so med seboj povezani preko matrik ter vhodno-izhodnih enot, kar omogoča zasnovo zelo kompleksnih digitalnih sistemov brez potrebe po razvoju namenskih integriranih vezij (Application-Specific Integrated Circuit – ASIC).

FPGA-ji se uporabljajo na številnih področjih – od obdelave podatkov v realnem času, vzporedne obdelavi podatkov, implementacije različnih algoritmov ter mikroprocesorskih arhitektur (npr. RISC-V), do prenosa velikih količin podatkov pri visokih hitrostih. Vpeljava FPGA naprav v gospodinjstvih omogoča integracijo različnih senzorjev (npr. za temperaturo, gibanje ali svetlobo), izvajanje inteligentnih algoritmov za nadzor naprav (ogrevanje, hlajenje, razsvetljava) ter upravljanje komunikacijskih protokolov, kot so ZigBee, Z-Wave in Wi-Fi, ki povezujejo pametne naprave v en sistem.

Ker so FPGA vezja razmeroma redko uporabljajo na področju avtomatizacije doma oziroma pri krmiljenju posameznih funkcionalnosti, smo v tej raziskovalni nalogi preučili okolja, v katerih bi takšna vezja lahko pokazala svoj polni potencial. Izkazalo se je, da bi se FPGA-ji zaradi svoje cenovne dostopnosti, velikega števila vhodno-izhodnih priključkov ter visoke prilagodljivosti najbolje izkazali v centraliziranih vgrajenih sistemih, kjer bi na novo razvita naprava omogočala upravljanje različnih podsistemov gospodinjstva z ene osrednje točke.

Platforme

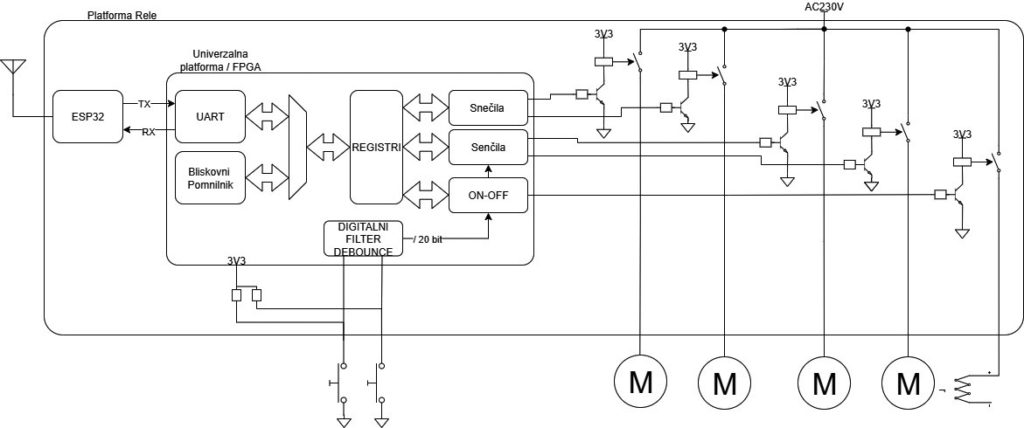

V okviru našega projekta smo zasnovali rešitev, pri kateri bo vezje FPGA prevzelo nalogo krmiljenja različnih sistemov v stavbi, vključno z razsvetljavo, senčili in ogrevanjem. Cilj je zagotoviti učinkovito, prilagodljivo in zanesljivo avtomatizacijo, ki omogoča optimizacijo porabe energije ter izboljšanje udobja uporabnikov.

Univerzalna FPGA Platforma

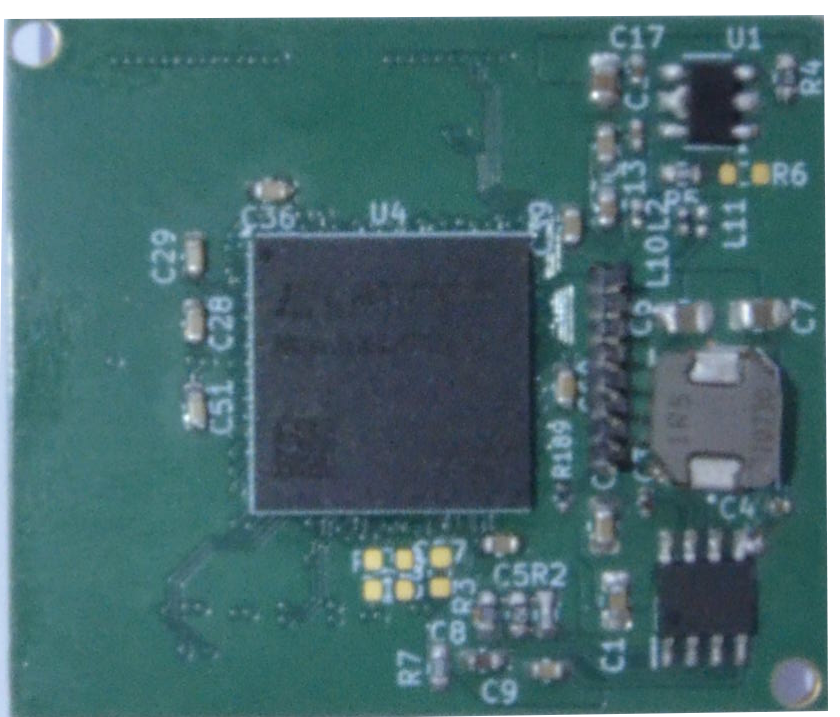

Sprva bomo začeli z osnovno FPGA platformo, ki predstavlja univerzalno ali glavno enoto sistema (Slika 1). Ta platforma bo imela sposobnost krmiljenja vseh prej omenjenih funkcij, kot so razsvetljava, senčil in ogrevanja. V našem primeru smo izbrali FPGA vezje MachXO5 [1] (LFMXO5-25-7BBG256C) proizvajalca Lattice, ki v enem ohišju združuje programirljivo logiko in FLASH pomnilnik. Takšna arhitektura omogoča konfiguracijo vezja FPGA in shranjevanje aplikativnih podatkov na enem mestu, kar poenostavlja razvoj in povečuje zanesljivost sistema.

Univerzalna enota, ki predstavlja osnovo našega sistema, vključuje 85 priključkov s priključki z razmikom 1,27 mm. Od teh so štirje priključki rezervirani za napajanje: dva za 5 V in dva za ozemljitev. Na voljo sta tudi dva dodatna priključka, ki omogočata napajanje osnovne plošče s 3,3 V oziroma 1,8 V, s čimer je omogočena fleksibilnost pri povezovanju različnih perifernih modulov. Preostalih 79 priključkov je namenjenih uporabniškim funkcionalnostim, kot so digitalni in analogni vhodi/izhodi, komunikacijski vmesniki (npr. UART, SPI, I²C) ter druge aplikacije, ki jih sistem potrebuje za krmiljenje razsvetljave, senčil in ogrevanja. Takšna zasnova omogoča modularnost in razširljivost sistema glede na potrebe končne aplikacije.

Platforma za razsvetljavo

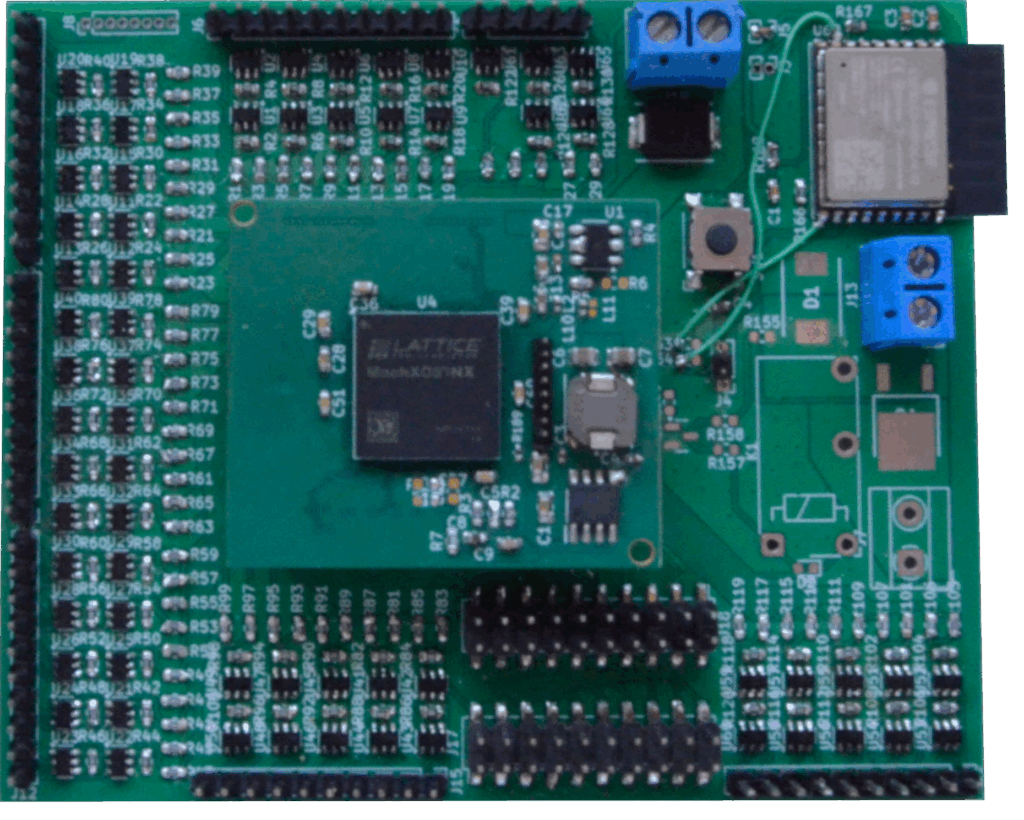

Po razvoju univerzalne FPGA enote smo nadaljevali z razvojem namenske enote za krmiljenje razsvetljave v gospodinjstvu. Na podlagi izvedene raziskave, ki je pokazala, da se vezja FPGA najbolje obnesejo kot centralne enote v sistemih za avtomatizacijo doma, smo zasnovo krmiljenja razsvetljave prilagodili tej ugotovitvi.

Namesto klasičnega pristopa z izmenično napetostjo 230 V, smo se odločili za uporabo enosmerne napetosti 48 V, ki jo napeljujemo od krmilne enote neposredno do posameznih svetil. Ta pristop omogoča večjo varnost, boljšo energetsko učinkovitost ter natančnejše krmiljenje vsake posamezne žarnice.

Za regulacijo svetilnosti posameznih žarnic uporabljamo pulzno širinsko modulacijo (PWM) v kombinaciji s tokovno krmiljenimi vezji, kot so vezja iz serije NCR321U [2]. Svetilnost je določena s tokom, ki ga omogoča vezje NCR321U v povezavi z zunanjim uporom ter dolžino PWM impulza, ki odpira in zapira bipolarni tranzistor v vezju. V našem primeru smo uporabili zunanji upor z upornostjo 13 Ω, kar določa maksimalni tok do 50 mA na žarnico.

PWM signal, ki se uporablja za krmiljenje svetilnosti posameznih žarnic, je generiran s pomočjo digitalnih komponent, integriranih v FPGA vezje. Digitalno vezje temelji na zasnovi končnega avtomata (FSM – Finite State Machine) in določa dolžino pulza glede na vhodne parametre.

Dolžina PWM pulza je odvisna od več dejavnikov, med katerimi sta ključna začetno stanje sistema in interakcija uporabnika. Začetno stanje je definirano z registri, ki hranijo informacije o trenutni konfiguraciji svetila. Ob pritisku tipke se svetilo vklopi ali izklopi. V primeru daljšega pritiska na tipko se intenzivnost svetilnosti poveča ali zmanjša.

V našem primeru sistem krmili skupno 65 svetil, ki se upravljajo preko 20 stikalnih tipk. Vsaka tipka lahko krmili eno ali več svetil hkrati, pri čemer je povezava med tipkami in svetili definirana preko vsebine registrov v FPGA vezju. Takšna zasnova omogoča fleksibilno konfiguracijo, saj lahko funkcionalnost posamezne tipke prilagodimo glede na potrebe uporabnika ali prostorsko razporeditev svetil.

Tak pristop omogoča dinamično upravljanje svetil, saj uporabnik s preprostim pritiskom na tipko neposredno vpliva na svetlobni izhod. FPGA vezje s svojo vzporedno obdelavo podatkov omogoča hitro odzivnost in natančno generacijo PWM signalov, kar je ključnega pomena za gladko regulacijo svetilnosti brez utripanja.

Platforma za senčila in ogrevanje

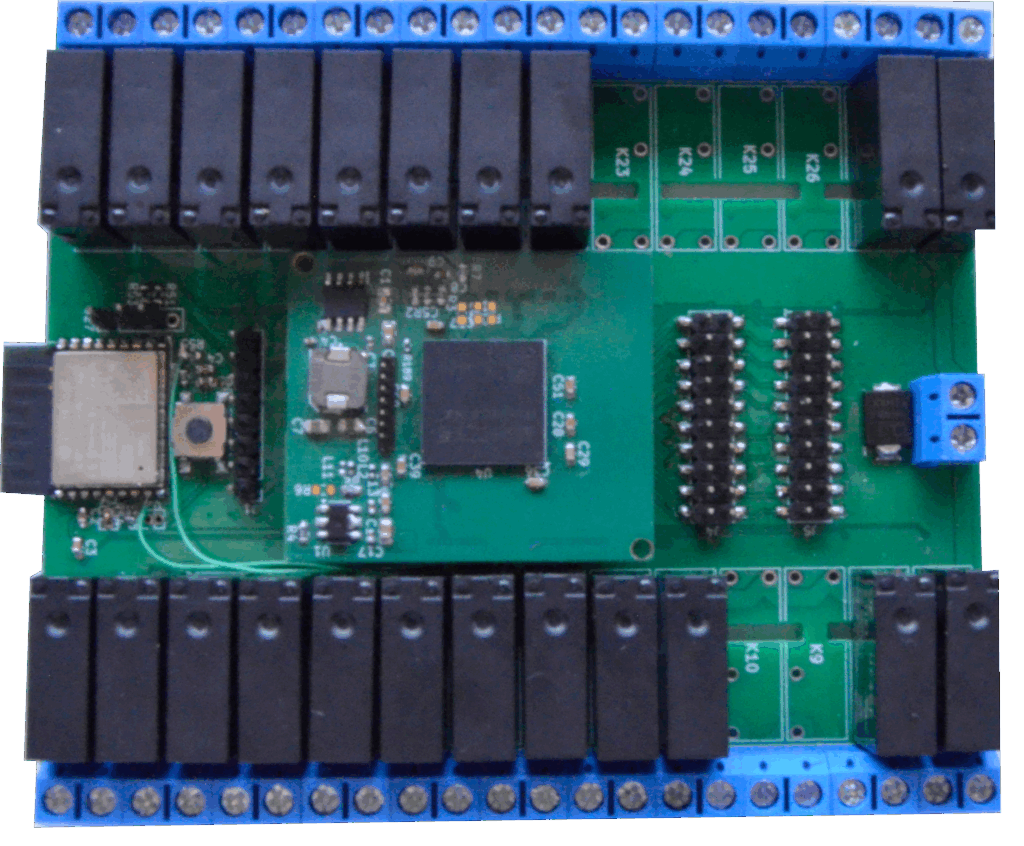

Naslednji korak raziskave je bil razvoj krmilne enote, ki je namenjena upravljanju senčil in nadzoru temperature. Omenjena enota je bila zasnovana preprosteje, saj vsebuje le relejne elemente, ki jih krmilijo bipolarni tranzistorji. Podobno kot v prejšnjem primeru, je tudi tukaj FPGA s svojo digitalno logiko, ki preko vhodno-izhodnih priključkov krmili bipolarne tranzistorje, le-ti pa omogočajo tok skozi releje, kar je povzročilo njihovo preklapljanje.

Za uravnavanje temperature je bil uporabljen temperaturni senzor EM38 podjetja TEM Čatež, ki je bil neposredno povezan z FPGA vezjem. Digitalna logika v FPGA vezju je bila razmeroma preprosta in je delovala po principu »ON-OFF«. Ko je tipalo zaznalo ustrezno temperaturo, se je rele aktiviral in omogočil delovanje grelnega elementa. Glavna prednost tega pristopa je možnost vklopa oziroma izklopa ogrevanja preko registrov znotraj FPGA vezja.

Nadzor senčil je bil nekoliko bolj zahteven, saj smo v tem primeru uporabili končni FSM avtomat, ki je omogočal natančno upravljanje senčil prek stenskih stikal in registrov. Za posamezno senčilo sta bila uporabljena dva releja (za dvig in spust) ter vsaj dva vhodna signala, ki določata smer gibanja. Vsako senčilo ima s pomočjo časovnikov določeno najvišjo in najnižjo točko, kar preprečuje mehanske poškodbe (npr., da se ob spustu senčila ne poškodujejo rastline na okenski polici).

Ob zagonu sistema (npr. po izpadu električne energije) avtomat najprej samodejno poišče referenčno točko, ki je najvišji položaj senčila. Ko je ta točka dosežena, sistem preide v stanje »IDLE« in omogoči uporabniško upravljanje. Nato uporabnik lahko s kratkim pritiskom na tipko popolnoma dvigne ali spusti senčilo, daljši pritisk pa omogoča nastavitev poljubne vmesne višine.

Podobno kot pri sistemu razsvetljave, lahko tudi pri krmiljenju senčil katerakoli priključena tipka aktivira funkcijo, če je to omogočeno preko FPGA registrov. Takšna zasnova omogoča centralizirano upravljanje vseh senčil, enostavno razširitev sistema in možnost vključevanja dodatnih funkcij (npr. avtomatsko zapiranje ob previsoki temperaturi ali ob zaznavi sončne svetlobe).

Krmiljenje razsvetljave, senčil in ogrevanja

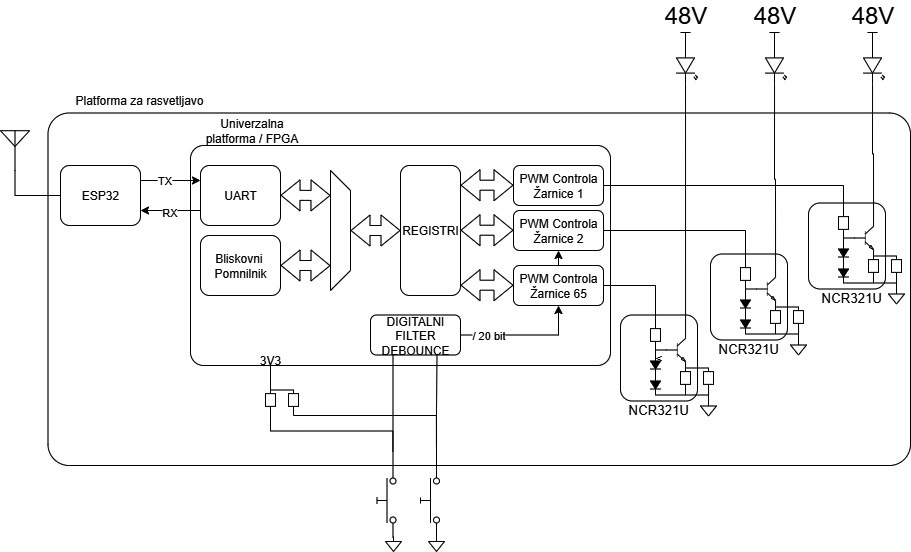

Do sedaj je bil poudarek predvsem na aplikativnih vidikih sistema, medtem ko je področje krmiljenja bilo manj obravnavano. Krmiljenje FPGA vezja je ključno za zagotavljanje pravilnega delovanja, prilagodljivosti in zanesljivosti celotne arhitekture. V nadaljevanju predstavljamo konceptualni pristop, ki temelji na dveh neodvisnih metodah konfiguracije registrov, ter opisujemo vlogo komunikacijskega mostu ESP32 [3] pri povezovanju uporabnika z napravo. FPGA omogoča konfiguracijo aplikacij preko registrov, ki definirajo ključne parametre delovanja:

- Konfiguracija preko FLASH pomnilnika

V tem pristopu so nastavitve shranjene v FLASH pomnilniku, kar omogoča avtonomno delovanje naprave. Ob zagonu naprave se podatki iz FLASH pomnilnika prenesejo v ustrezne registre, kar zagotavlja deterministično in ponovljivo konfiguracijo. Ta metoda je posebej primerna za aplikacije, kjer sta zahtevani visoka stopnja robustnosti in minimalna interakcija z zunanjimi sistemi. - Konfiguracija preko UART komunikacije

Drugi pristop temelji na dinamični konfiguraciji preko UART serijskega vmesnika. Uporabnik lahko z uporabo UART protokola zapisuje in bere vrednosti registrov. Poleg tega je omogočena sinhronizacija sprememb s FLASH pomnilnikom, ki zagotavlja trajnost nastavitev po ponovnem zagonu naprave.

Ker predstavljeni sistem vključuje dve aplikativni napravi, smo na vsako namestili ESP32 modul. Njegova primarna funkcija je pretvorba podatkov iz Wi-Fi protokola v UART protokol, ki omogoča oddaljeno upravljanje registrov v FPGA vezju. ESP32 tako deluje kot vmesnik med uporabnikom in pristop odpira možnosti za integracijo v IoT okolja ter omogoča nadzor in diagnostiko na daljavo.

Analogne komponente vgrajene v FPGA

Poleg že omenjene FPGA aplikacije smo v FPGA umestili tudi digitalne filtre za odpravo preskokov stikal (debounce) neposredno v logično strukturo naprave. S tem smo klasični RC filter nadomestili z digitalnim filtrom.

Rešitev prinaša več ključnih prednosti:

Zmanjšana kompleksnost tiskanega vezja: Odstranitev analognih komponent kot so upori in kondenzatorji, poenostavi zasnovo vezja ter zmanjša število potrebnih elementov.

Manjša fizična velikost naprave: Integracija funkcionalnosti v FPGA omogoča bolj kompaktno izvedbo, kar je posebej pomembno pri prostorsko omejenih aplikacijah.

Večja prilagodljivost: Digitalni filter je mogoče enostavno prilagoditi ali nadgraditi z modifikacijo kode HDL, brez sprememb strojne opreme.

Deterministično delovanje: Digitalna implementacija zagotavlja ponovljivost in stabilnost odziva, neodvisno od tolerance analognih komponent.

Implementacija

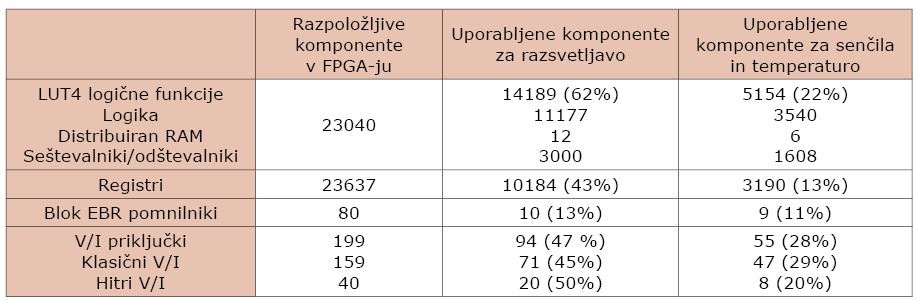

Za realizacijo našega projekta smo izbrali Lattice MachXO5-25 (LFMXO5-25-7BBG256C), ki je najmanjši model iz družine MachXO5 FPGA vezij. Kljub svoji kompaktni zasnovi se je izkazal kot popolnoma primerno integrirano vezje za vse predvidene aplikacije.

Konfiguracijski pomnilnik tega FPGA vezja temelji na SRAM pomnilnih celicah, ki omogočajo programiranje na dva načina: preko zunanjega JTAG vmesnika ali, v našem primeru preko vgrajenega FLASH pomnilnika. Slednji pristop zagotavlja avtonomno delovanje naprave ob vsakem zagonu.

Zaradi razmeroma nizke kompleksnosti naših aplikacij smo uporabili le osnovne logične komponente. Za realizacijo kombinacijskih logičnih funkcij smo uporabili LUT (Look-Up Table) elemente in sekvenčna vezja. Spodnja tabela prikazuje razpoložljive logične vire v izbranem FPGA vezju ter njihovo dejansko izkoriščenost v naših aplikacijah.

Pomemben vidik vrednotenja razvitih krmilnih enot je njihova energetska učinkovitost. Meritve porabe moči so pokazale, da obe krmilni enoti v mirovnem stanju, torej brez aktivnih bremen, porabita približno 50 mA pri napajalni napetosti 5 V, kar ustreza porabi moči 250 mW na enoto, kar vključuje Univerzalno FPGA platformo in aplikativno platformo).

Pri relejni krmilni enoti, namenjeni upravljanju senčil in ogrevanja, pa se energetska poraba ob polni obremenitvi bistveno poveča. Ko so vsi releji simultano aktivirani, se poraba toka poveča na 750 mA, kar pri napetosti 5 V pomeni skupno porabo moči 3,75 W. Ta poraba je pričakovana, saj elektromehanični releji za svoje delovanje potrebujejo relativno visoke tokove za vzdrževanje magnetnega polja v tuljavi.

Kljub povečani porabi ob aktivaciji relejev, je sistem še vedno energetsko učinkovit, saj v tipičnih obratovalnih scenarijih niso vsi releji aktivirani hkrati. Povprečna poraba v realnih pogojih uporabe je zato bistveno nižja od izmerjene maksimalne vrednosti.

Poraba žarnice ni vključena v meritve, saj žarnice uporabljajo napajalno napetost 48 V. Toda maksimalna poraba žarnice skupaj z diodnim krmilnikom NCR321U je 2,4 W oziroma 288 lm (žarnice so po prostorih razporejene z razmakom 1,5 m). Zaradi majhne porabe žarnice, te ne potrebujejo dodatnega hladilnega telesa za odvajanje toplote.

Zaključek

S kombinacijo ESP32 mikrokontrolerjev in FPGA vezij uporabljenih v našem projektu, je mogoče razviti učinkovite in prilagodljive platforme za avtomatizacijo gospodinjstev. Razviti sistem je pokazal, da takšna arhitektura omogoča visoko stopnjo fleksibilnosti pri krmiljenju različnih podsistemov doma.

Kljub ugotovljenim prednostim analiza kaže, da se FPGA vezja najbolje izkažejo v centraliziranih aplikacijah. Ta omejitev izhaja predvsem iz fizičnih dimenzij FPGA vezij ter njihove cenovne dostopnosti, ki postane ekonomsko upravičena šele pri večjem številu integriranih funkcionalnosti na eni krmilni enoti. Za decentralizirane sisteme z manjšim številom vhodno-izhodnih signalov ostajajo klasični mikrokontrolerjev bolj primerna rešitev.

Reference

[1] MachXO5-NX Family FPGA-DS-02102-2.1

[2] NCR320U / NCR321U 250mA LED driver in SOT457 Rev. 1 – 11 December 2018

[3] ESP32-C3 Series Datasheet Version 2.2 Ultra-Low-Power SoC with RISC-V Single-Core CPU 2.4 GHz Wi-Fi (802.11b/g/n) and Bluetooth® 5 (LE) Optional 4 MB flash in the chip’s package QFN32 (5×5 mm) package