Kot pove že ime, so gonilniki analogno-digitalnega pretvornika [1] (ADC) posebni ojačevalniki, ki so zasnovani posebej za delovanje skupaj z ADC-ji, vključno z arhitekturami, ki temeljijo na zaporednem približevanju (angl. successive approximation), vodilu in delta-sigma pretvorbi.

Ti posebni ojačevalniki so kritične komponente vezja, ki omogočajo, da ADC deluje s polno zmogljivostjo, kot bo raziskano v naslednjih razdelkih.

Kaj je gonilnik analogno-digitalnega pretvornika in zakaj ga potrebujem?

Kot pove že ime, so gonilniki analogno-digitalnega pretvornika [1] (ADC) posebni ojačevalniki, ki so zasnovani posebej za delovanje skupaj z ADC-ji, vključno z arhitekturami, ki temeljijo na zaporednem približevanju, vodilu in delta-sigma pretvorbi. Ti posebni ojačevalniki so kritične komponente vezja, ki omogočajo, da ADC deluje s polno zmogljivostjo, kot bo raziskano v naslednjih razdelkih. Potreba po kondicioniranju analognih signalov, vključno z ADC-ji, še naprej narašča, saj senzorji postajajo vedno bolj razširjeni na različnih končnih trgih. Ti končni trgi vključujejo:

- Komunikacije

- Medicina

- Širokopotrošni izdelki

- Industrija

- Avtomobilska industrija

Pri ADC-jih je tržni trend v smeri višjih ločljivosti in hitrejših naprav, saj so stroški takšnih rešitev dostopnejši.

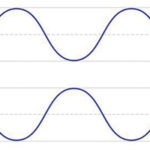

Razumevanje ADC vhodov

Preden razpravljamo o tehničnih funkcijah, ki jih potrebuje ADC gonilnik, je potreben kratek pregled vhodne arhitekture današnjega ADC. Diferencialni signal je mogoče definirati kot dve vozlišči, ki imata enake, pa vendar v fazi nasprotne signale okoli fiksne točke (nivo skupnega načina). Dve signalni vozlišči se običajno imenujeta pozitivna in negativna (neinvertirajoča in invertirajoča), kot je prikazano na sliki 1.

V zgornjem primeru je polna vhodna napetost 5 V od vrha do vrha diferencialno, pri čemer signal na vsakem priključku niha 2,5 V od vrha do vrha. Raven skupnega načina v tem primeru je 2,5 V. Večina današnjih visokozmogljivih ADC-jev vsebuje diferencialno vhodno arhitekturo, saj zagotavlja vrhunsko zmogljivost (glede na enosmerne vhode). Te prednosti delovanja vključujejo zmožnost dušenja sofaznega šuma in sofaznih signalov motenj ter povečanje dinamičnega razpona za 6 dB (ali za faktor 2).

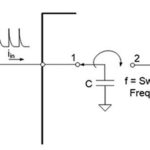

ADC-ji lahko predstavljajo še posebej težaven izziv za sistemske razvojnike, saj ponujajo vrsto različnih arhitektur vzorčenja vhoda, ki jih je treba upoštevati na ravni sistema. Za namene te razprave bo poudarek na ADC-jih, ki uporabljajo “s-C” strukturo s preklapljanjem kondenzatorja (angl. switched-Capacitor) za izvedbo vzorčenja vhoda. V svoji najbolj osnovni obliki je ta vhodna struktura sestavljena iz relativno majhnega kondenzatorja in analognega stikala, kot je prikazano na sliki 2.

Ko je stikalo postavljeno v položaju 1, se kondenzator napolni na napetost vzorčnega vozlišča, v tem primeru VS. Stikalo nato preklopi v položaj 2, kjer se akumulirani naboj na kondenzatorju za vzorčenje nato prenese na preostali del vzorčnega vezja. Nato se postopek začne znova.

Vhod “n-C” brez ojačevalnika, kot je opisan zgoraj, lahko povzroči pomembne težave na ravni sistema. Tok, potreben za polnjenje kondenzatorja na ustrezno napetost, se mora napajati iz zunanjega vezja, priključenega na vhod ADC. Ko se kondenzator preklopi na vozlišče za vzorčenje (položaj stikala 1 na sliki 2), bo za začetek polnjenja kondenzatorja potrebna velika količina toka. Velikost tega trenutnega toka je funkcija velikosti kondenzatorja za vzorčenje, frekvence, pri kateri se kondenzator preklopi, in napetosti, ki je prisotna na vozlišču za vzorčenje. Ta preklopni tok lahko opišemo z naslednjo enačbo:

V zgornjem primeru je C kapacitivnost kondenzatorja za vzorčenje, V je napetost, prisotna na vozlišču za vzorčenje (v tem primeru označena kot VS), f je frekvenca, pri kateri se stikalo za vzorčenje vklopi in izklopi. Ta preklopni tok povzroči visoke tokovne konice na vozlišču za vzorčenje, kot je prikazano na sliki 2.

Pri načrtovanju analognega vezja pred A/D pretvornikom je treba upoštevati posledice tega toka preklopa. Ko ta tok teče skozi kateri koli upor, bo prišlo do padca napetosti, kar bo povzročilo napetostno napako na vzorčnem vozlišču A/D pretvornika. Popačenje se lahko pojavi tudi, če vhodno vozlišče ni v popolnoma mirovnem stanju pred naslednjim ciklom vzorčenja.

Rešitev: ADC gonilniki

Vzdrževanje zahtevane celovitosti signala senzorja, da bi v celoti izkoristili te višje ločljivosti, za hitrejši ADC postane to zelo zahtevno. Ko se povečata ločljivost in hitrost ADC-ja, postanejo učinki šuma in popačenja iz signala senzorja bolj opazni. Pri višjih hitrostih ADC vzorčenja je treba zagotoviti, da se je vhodni signal umiril pred dogodkom vzorčenja in da se signali z večjo pasovno širino ne preslikajo nazaj v pasovno širino signala, ki vas zanima.

Da bi premagali te izzive kondicioniranja signala, številne ADC aplikacije potrebujejo ADC gonilnik, ki zagotavlja zadostno poravnavo in dušenje zrcalnih frekvenc. Kot je opisano zgoraj, večina sodobnih ADC izvaja diferencialno vhodno arhitekturo. Ena od glavnih funkcij ADC gonilnika je zagotoviti pretvorbo iz nesimetričnega v diferencialno obliko vhodnega signala.

Druga funkcija ADC gonilnika je ojačenje vhodnega signala, s čimer izolira preostali del vezja od generiranja naboja na vhodnem vozlišču ADC. ADC gonilnik zagotavlja takojšnje polnjenje kar zagotovi, da je vzorčno vozlišče skladno poravnano v času , s čimer se zmanjša kakršno koli popačenje, povezano z poravnavo.

Večina ADC gonilnikov za ojačevalnike ponuja tudi fizični priključek, ki uporabniku omogoča sofazni premik po nivoju napetosti . Ta funkcija je idealna za zagotovitev, da je nastali diferenčni signal centriran v območju vhodne ADC napetosti, s čimer se poveča dinamični razpon.

Končno, podobno kot večina komponent ojačevalnika, lahko ADC gonilniki zagotovijo ojačenje vhodnega signala in aktivno filtriranje. Treba je opozoriti, da je večina ADC gonilnikov določena z relativno nizkim ojačenjem, običajno le 1 ali 2 V/V. Z ohranjanjem nizkega ojačenja v zaprti zanki ojačevalnika je ojačenje v zanki maksimalno, kar ima za posledico najmanjše popačenje. Na primer, če ima ojačevalnik ojačenje odprte zanke 100 dB in je konfiguriran za ojačenje v zaprti zanki 200 ali 46 dB, ostane le 54 dB rezerve ojačenja odprte zanke, da se zagotovi linearnost, ali približno en del v 500. Zato je dobro imeti ločeno ojačevalno stopnjo, ki se nahaja blizu vira signala.

Da bi kar najbolje izkoristili vaš pretvornik signalov, mora ADC gonilnik optimizirati zmogljivost, hkrati pa izvornemu signalu dodati zanemarljivo popačenje, šum in napake časovne poravnave. Diferencialni gonilnik MCP6D11 [2] je posebej zasnovan za povečanje zmogljivosti hitrih ADC-jev, kot je MCP33131 [3], ki je 16-bitni 1MSPS SAR ADC. Za primer, kako ti dve napravi delujeta skupaj, da bi povečali zmogljivost, si oglejte razvojno ploščo MCP331x1 Evaluation Board (ADM00873) [4].

Viri:

https://www.microchip.com/en-us/products/data-converters/analog-to-digital-converters

https://www.microchip.com/wwwproducts/en/MCP6D11

https://www.microchip.com/en-us/product/MCP33131D-10

https://www.microchip.com/en-us/development-tool/ADM00873

Opomba: Ime in logotip Microchip sta registrirani blagovni znamki podjetja Microchip Technology Incorporated v ZDA in drugih državah. Vse druge blagovne znamke, ki so morda tu omenjene, so last njihovih podjetij.

Microchip Technology Inc.

Avtor: Kevin Tretter