Microchip Technology Inc

Microchip Technology Inc

Avtor: Manu Venkategowda

2019_271_18

Manu Venkategowda iz podjetja Microchip Technology Inc. razlaga, kako lahko konfigurabilna logična celica poenostavi implementacijo kompleksnih funkcij v mikrokontrolerju.

Včasih lahko nekaj preprostega prinese velike koristi. Večina ugnezdenih inženirjev uporablja različne signale ali logiko za obravnavanje potreb končnih aplikacij. Za reševanje teh potreb se zatekajo k oblikovanju kompleksne logike. Kaj pa, če bi obstajal preprost način, da bi naredili nekaj bolj zapletenega? Nekateri mikrokontrolerji imajo prilagodljive periferne enote za izvajanje funkcij, potrebne za kompleksne aplikacije.

To je tisto, kjer pride na vrsto konfigurabilna logična celica (Configurable Logic Cell CLC). CLC periferija je bila dodana v nabor perifernih naprav za Microchip PIC ® mikrokontrolerjev (MCUs) in omogoča uporabnikom, da oblikujejo preprosto funkcijo, ki lahko služi kot vmesnik za MCU. Ta CLC periferna naprava uporabniku omogoča, da določi kombinacije signalov kot vhodne podatke za logično funkcijo in uporabi logični izhod za nadzor drugih perifernih naprav in IO priključki, kar uporabnikom omogoča prilagodljivost pri oblikovanju funkcije po svoji izbiri.

Da bi bile stvari enostavne, je CLC podprt v konfiguratorju kode MPLAB® (MCC) podjetja Microchip. To razvijalcu omogoča, da enostavno povleče in spusti logična vrata, da poveže vhode in izhode v obliki GUI, in s klikom na gumb ustvari kodo C, kar močno poenostavi izvajanje CLC modulov.

Od jedra neodvisna periferija (Core Independent Peripherals CIP) opravlja svoje naloge brez dodatne kode ali nadzora CPU, da bi ohranila njihovo delovanje. CLC je takšen CIP, ki poenostavlja izvajanje zapletenih nadzornih sistemov in hkrati omogoča razvijalcem veliko fleksibilnosti pri načrtovanju, tako da se CPU obremeni in tako izboljša zmogljivost mikrokontrolerja. Nadaljujte z branjem, da boste izvedeli, kako se lahko CLC uporablja za zaznavanje faz signala, komplementarno generiranje signalnih oblik ali za spremljanje več parametrov v aplikaciji. S široko paleto vhodov, sprožilcev in izhodov so možnosti pri CLC neskončne.

Pregled

CLC je uporabniško nastavljiv periferni sistem, podoben programabilni logični napravi (PLD), vendar integriran v mikrokontroler. Notranji in zunanji vhodi se lahko izberejo kot vhodni podatki za CLC. CLC prejme vhode iz drugih perifernih naprav ali iz vhoda. Nato izvede predvideno logično operacijo in zagotavlja izhod, ki se lahko uporablja za krmiljenje drugih zunanjih naprav ali drugega IO priključka.

CLC lahko sprejema signale, kot je notranji taktni signal, izhod druge periferije in perifernega dogodka, kot je časovni vhod. Izbrani vhodni signali se lahko usmerijo na želeno logično funkcijo skozi stopnjo signalizacije.

CLC podpira različne logične funkcije, kot so AND, OR, NOT, XOR, NAND, NOR in XNOR. V CLC so izhodi faze odčitavanja podatkov vhodi v fazo izbire logičnih funkcij. Stopnja izhodne polaritete je zadnja stopnja v CLC in lahko izberete želeno polariteto.

CLC se lahko uporablja kot samostojna periferna enota pri izvajanju sekvenčnih in kombinacijskih logičnih funkcij, s čimer se omogočajo hitri sprožilci dogodkov in odzivi. Uporablja se lahko tudi z drugimi perifernimi napravami, da pomaga razširiti njihove zmožnosti, z omogočanjem izvajanja kompleksnih funkcionalnosti po želji v strojni opremi.

Ker je CLC neodvisna periferna enota, CLC učinkovito zmanjša zahtevo za pasovno širino CPU za aplikacijo, tako da prenaša veliko preprostih in logičnih odzivov dogodkov iz CPU na periferno. Prav tako zmanjšuje zahteve za Flash in RAM, saj programski algoritmi niso potrebni.

Logične funkcije, ki se izvajajo v strojni opremi, imajo hitrejši odziv dogodka v primerjavi z logičnimi funkcijami, ki se izvajajo v programski opremi. Poleg tega CLC podpira višjo stopnjo integracije brez zunanjih komponent, kar zmanjšuje celotno velikost tiskanega vezja.

Fazni detektor

Vsestranske funkcije in preprostost CLC razširjajo zmožnosti oblikovanja PIC MCU. Dober primer, ki dokazuje zmožnosti CLC, je v faznem detektorju. Fazni detektor se lahko uporablja za številne aplikacije, vključno z merjenjem razdalj. Deluje po načelu, da ko je neprekinjen VF val oddan proti cilju, je razdalja do cilja sorazmerna s faznim premikom med oddanimi in prejetimi valovi. CLC se lahko uporablja za merjenje fazne razlike med dvema signaloma iste frekvence. Oddani in prejeti valovi se uporabljajo kot vhodni podatki za CLC in fazna razlika med dvema signaloma na izhodu CLC se lahko uporabi za izračun razdalje med virom in tarčo.

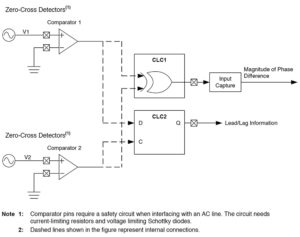

Pri izvedbi faznega detektorja z uporabo CLC se lahko logična funkcija IN-ALI v CLC uporabi za izvajanje funkcije XOR za merjenje velikosti fazne razlike in logična funkcija D-Flip Flop (D-FF) pomaga pri pridobivanju informacije o prehitevanju in zamiku signalov. Poleg kvadratnih signalov je mogoče meriti fazo med drugimi tipi analognih signalov, kot so sinusni signali. Slika 1 prikazuje konfiguracijo faznega detektorja z uporabo CLC.

Signala vira, katerih fazno razliko je treba izmeriti, se dovajata na vhoda v dva komparatorja, ki sta konfigurirana kot detektorja prehoda preko ničle (zero-cross detectors ZCD). ZCD pretvorijo vhodne analogne signale v kvadratne signale enake frekvence. Če so izvorni signali kvadratni signali, potem ZCD niso potrebni. Kvadratni signali so interno preusmerjeni kot vhodi v več modulov CLC.

CLC1 in periferni vhodni zajem (IC) se uporabljata za določanje velikosti fazne razlike. CLC1 je konfiguriran v logični funkciji IN-ALI, iz katere je izpeljana XOR-funkcija. XORiran izhod CLC1 je zunanje povezan kot vir signala na IC. Širina impulza XOR izhoda daje velikost fazne razlike med obema signaloma in jo meri IC. Če izhod CLC1 ne proizvaja signala, so izvorni signali v fazi.

Za določitev informacij o fazi prehitevajočega in zamaknjenega signala dveh vhodnih signalnih oblik je CLC konfiguriran v načinu D-FF z enim kvadratnim signalom in uporabljenim D vhodom, drugi pa je uporabljen kot takt. Izhod CLC2, ki je visok ali nizek, bo določil, ali D vhod vodi ali zaostaja v fazi glede na taktni vhod. Merjenje faznega kota med dvema signaloma iste frekvence je koristno pri številnih aplikacijah, vključno z merjenjem, digitalnimi energetskimi sistemi, komunikacijskimi in medicinskimi instrumenti.

Komplementarni generator signalov

Drug način uporabe CLC je v komplementarnem generatorju signalov (complementary waveform generator CWG). CWG proizvaja dopolnilno signalno obliko s krmiljenjem mrtvega pasu iz vhodnega vira. Med dvema signaloma se vstavi časovno mrtvo območje, da se prepreči pretočni tok v različnih aplikacijah napajanja.

Ta aplikacija ponazarja uporabo zaznavanja robov CLC-a in zmožnosti prekinitev pri ustvarjanju komplementarnih signalnih oblik z enim samim zajemi / primerjaj / PWM (SCCP) modulom kot vhodnim virom.

Pogosto aplikacije, kot je nadzor motorja, zahtevajo več generatorjev oblik signalov, ki nadzorujejo njihovo delovanje. Modul za večkratno zajemanje / primerjavo / PWM (MCCP) lahko proizvaja komplementarne oblike signalov z neprekrivajočimi se signali s krmiljenjem mrtvega pasu na svojem izhodu. Če pa aplikacija zahteva več primerkov MCCP od tistih, ki so na voljo v napravi, se lahko uporabi SCCP v kombinaciji s CLC.

Periferne enote CLC z SCCP se lahko uporabijo za generiranje komplementarne oblike signala z zahtevanim mrtvim pasom, saj sam SCCP ne more ustvariti signalov, ki se ne prekrivajo.

Mrtvi pas se lahko doda tako za robno poravnan, kot za centriran SCCP izhod. Slika 2 prikazuje konfiguracijo CLC1, CLC2 in CLC3 za nadzor mrtvega pasu SCCP izhoda v načinu, ki je usklajen z robom.

Na primer, vezje pogona motorja s polnim mostičem lahko krmilimo z uporabo periferne enote MCCP z izhodom, ki proizvaja komplementarno obliko signala. Če pa je treba poganjati več takih vezij krmilnikov motorja polnim mostičem in če je na napravi na voljo dovoljšnje število perifernih MCCP naprav, je mogoče uporabiti SCCP v kombinaciji s CLC.

Spremljanje večjega števila parametrov

Pogosto aplikacije zahtevajo hkratno spremljanje različnih parametrov, kot so temperatura, tlak in vlažnost. Če bi ti parametri začeli prehajati zgornje ali spodnje meje, je treba sprejeti potrebne ukrepe za preprečitev katastrofalnih rezultatov.

Na voljo je več komparatorjev kot vhodni vir za CLC. V mikrokontrolerju se lahko komparator uporablja za spremljanje samo enega parametra. Izhod večjega števila komparatorjev se lahko kombinira z uporabo CLC, za nadzor večjega števila parametrov.

Potrebno je ukrepanje, kadar kateri koli ali vsi spremljani parametri presegajo določeno mejo. Slika 3 prikazuje konfiguracijo CLC za spremljanje dveh različnih parametrov.

V praksi ta aplikacija najde svojo uporabo pri spremljanju temperature in tlaka v industrijskem obratu, tako da je mogoče obrat ustaviti, če katerikoli od parametrov preseže vnaprej določen prag. Lahko se uporablja tudi za spremljanje napetostnih nivojev v načinu brezprekinitvenega napajanja brez povezave.

Zaključek

Dodajanje konfiguracijske logične celice v nabor perifernih naprav omogoča uporabnikom, da integrirajo enostavne logične zasnove v PIC mikrokontrolerju. Združevanje rezultatov različnih perifernih naprav povečuje zmogljivosti obstoječih zunanjih naprav in s tem širi obzorje aplikacij, ki jih lahko dosežejo periferne naprave.

Ker imajo logične funkcije, ki se izvajajo v strojni opremi, hitrejši odziv na dogodek v primerjavi z logičnimi funkcijami, ki se izvajajo v programski opremi, CLC pomaga izboljšati hitrost celotnega sistema. Zagotavlja tudi višjo stopnjo integracije brez potrebe po zunanjih logičnih vratih za izvajanje logičnih funkcij, s čimer se zmanjša število potrebnih delov in celotna velikost tiskanega vezja. CLC prav tako pomaga pri kombiniranju različnih signalov vhodnega vira z uporabo različnih logičnih vrat za izdelavo popolnoma različnih signalov.

Vse te prilagodljive vhode in izhode ter logične funkcije je preprosto izvajati z orodjem na osnovi uporabniškega vmesnika, ki se imenuje konfigurator kode MPLAB (MCC), ki bo ustvaril lahko berljivo C kodo za vašo aplikacijo.

Dodatni viri:

- Extending PIC MCU Capabilities Using CLC Application Note:

- http://ww1.microchip.com/downloads/en/AppNotes/00002133a.pdf

Opomba: Ime in logotip Microchip sta registrirani blagovni znamki podjetja Microchip Technology Incorporated v ZDA in drugih državah. Vse druge blagovne znamke, ki so morda tu omenjene, so last njihovih podjetij.