DigiKey

Avtor: Rolf Horn

Ciklično preklapljanje moči ima ključno vlogo pri zagotavljanju nemotenega delovanja elektronskih aplikacij, zlasti tistih, ki so nameščene na odmaknjenih območjih in se napajajo z baterijami.

Dejanje odklopa in ponovnega priklopa napajalnika lahko resetira sistem, ki je postal neodziven zaradi daljše nedejavnosti ali prekinitev sistema. Eden od učinkovitih in pogosto uporabljenih pristopov za preklapljanje moči je uporaba aktivnega nizkega izhoda nadzornega vezja za pogon vhodnega stikala MOSFET na visoki strani.

Monitorji napetosti ali nadzorna vezja lahko zagotovijo dve možnosti za svoj logični izhodni nivo: aktivni nizek in aktivni visok izhodni signal. To velja bodisi za izhodno topologijo push-pull oz. izhodno topologijo odprtega ponora s pull-up uporom.

Aktivno nizko, pri čemer je izhod nizek, ko je vhodni pogoj izpolnjen, in visok, ko vhodni pogoj ni izpolnjen.

Aktivno visoko, pri čemer je izhod visok, ko je vhodni pogoj izpolnjen, in nizek, ko vhodni pogoj ni izpolnjen.

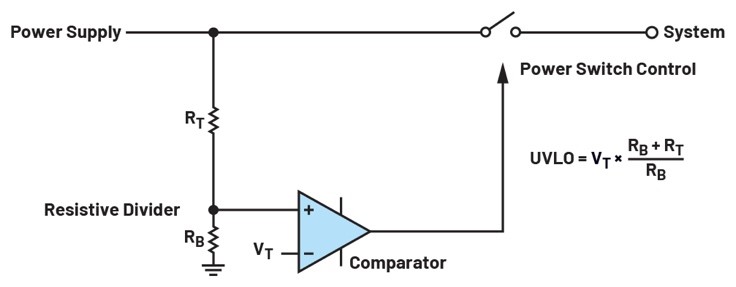

Nadzorna vezja nadzirajo sistemsko aktivnost s sledenjem napajalni napetosti ali uporabo nadzornih časovnikov za zaznavanje nedejavnosti ali oboje. Ko ti zaščitni ukrepi zaznajo težavo, se ciklično napajanje odpre in nato zapre pot med napajalnikom in nadaljnjim sistemom, zaradi česar gre mikrokontrolerska enota (MCU) v postopek reseta. Vhodno stikalo na visoki strani vezja (slika 1) se uporablja za krmiljenje napajanja nadaljnjega elektronskega sistema.

Vendar pa je bistvenega pomena, da izberete prave komponente in obravnavate morebitne izzive, kot sta ustvarjanje toplote in šum preklapljanja, ki sta lahko posledica cikličnega postopka preklapljanja.

Vendar pa je bistvenega pomena, da izberete prave komponente in obravnavate morebitne izzive, kot sta ustvarjanje toplote in šum preklapljanja, ki sta lahko posledica cikličnega postopka preklapljanja.

Stikalo za vklop na visoki strani vezja

Ciklično preklapljanje se lahko uporablja v različnih aplikacijah za izboljšanje zanesljivosti sistema in ublažitev morebitne škode, vključno z brezžičnimi oddajniki-sprejemniki, medicinskimi napravami, pametnimi napravami za dom, napajalniki in potrošniško elektroniko.

Polprevodniški tranzistorji s kovinskim oksidom (MOSFET) se pogosto uporabljajo pri cikličnem preklapljanju, ker imajo nizek upor pri vklopu, visoko hitrost preklapljanja in visoko vhodno impedanco.

Izhod iz nadzornega vezja lahko krmili vrata MOSFET-a in ga učinkovito vklopi ali izklopi za ciklično napajanje. Ta metoda zagotavlja optimalno zanesljivost sistema, tako da sistemu omogoči reset in obnovitev stanja neodzivnosti.

Razvijalci, ki uporabljajo ta pristop, imajo možnost uporabe N-kanalnih ali P-kanalnih MOSFET-ov, vendar mnogi raje uporabljajo P-kanalni pristop, saj so pogoji in vezje, potrebni za njihov vklop in izklop, manj zapleteni kot pri N-kanalnih MOSFET-ih.

Za P-kanalni MOSFET mora biti napetost vrat nižja od izvorne napetosti, da se vklopi, medtem ko mora biti pri N-kanalnem MOSFET-u napetost vrat višja od izvorne napetosti, da se vklopi.

Ko se N-kanalni MOSFET uporablja kot vhodno stikalo na visoki strani, nizka napetost vrat povzroči, da se stikalo odpre in prekine napajanje. Medtem ko N-kanalni MOSFET-i na splošno ponujajo boljšo učinkovitost in zmogljivost, je v tem kontekstu potrebno dodatno vezje, kot je črpalka naboja, da se ustvari pozitivna napetost na vratih (VGS), da zagotovite, da stikalo znova priključi napajanje v celoti.

To dodatno vezje ni potrebno pri uporabi P-kanalnega MOSFET-a, ki ga je mogoče vklopiti z negativnim VGS, kar poenostavlja zasnovo aplikacije, čeprav to pomeni večjo odpornost na vklop in nižjo učinkovitost.

Implementacija P-kanalnega stikala na visoki strani

Pri P-kanalnem pristopu mora biti napetost na vratih za krmiljenje MOSFET-a nižja od napajalne vsaj za mejno napetost na vratih VGS(th), da omogočite pretok toka od vira do ponora. Poleg tega je treba zagotoviti, da napetost med ponorom in virom (VDS) deluje znotraj določenih meja, da zagotovite, da se tranzistor ne poškoduje.

Ko je aktivni nizki izhod nadzornega vezja povezan z vrati P-kanalnega MOSFET-a, OUT pin povleče vrata nizko, ko je podani prag presežen, kar aktivira povezljivost od napajalne napetosti do bremena. Ko napetost pade pod prag, gre OUT pin visoko in P-kanalni MOSFET se izklopi, kar odklopi breme od napajanja.

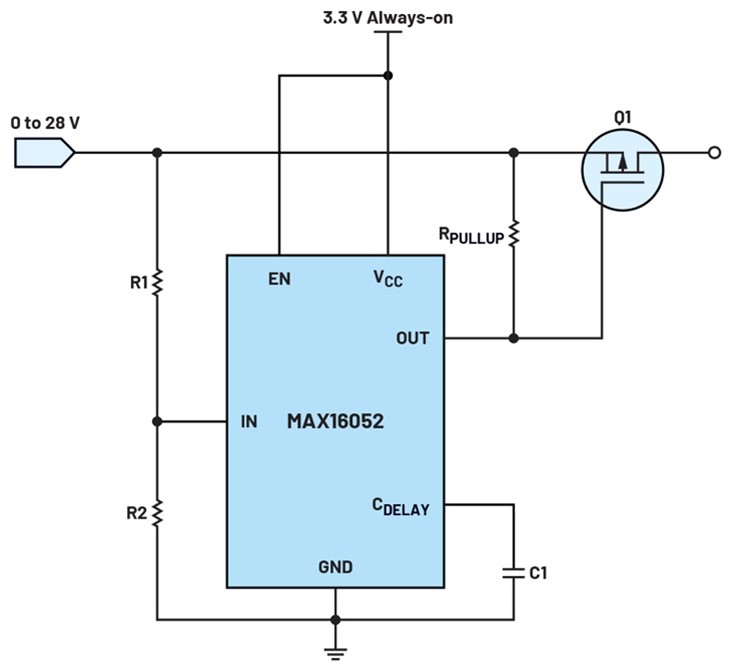

Razvijalci lahko ustvarijo prenapetostno zaščitno vezje, ki je zelo učinkovito, tako da neposredno povežejo OUT pin naprave z vrati P-kanalnega MOSFET-a. Ta robusten pristop, ki uporablja P-kanalni MOSFET kot stikalo na visoki strani, povezano z Analog Devices, Inc., upravljanje napajanja IC MAX16052 (slika 2), zagotavlja, da je breme priključeno na napajalno napetost.

Zunanji pull-up upor med nadzorovano napetostjo in vrati P-kanalnega MOSFET-a ohranja vrata visoko, ko je OUT pin z odprtim ponorom v stanju visoke impedance. OUT pin preide v stanje visoke impedance, ko nadzorovana napetost preseže prag, in izklopi P-kanalni MOSFET ter odklopi breme od napajalne napetosti. Nasprotno pa OUT pin povleče priključek vrat nizko, ko nadzorovana napetost pade pod prag.

MAX16052, skupaj z ADI MAX16053, sestavlja linijo manjših, nizkoenergijskih, visokonapetostnih nadzornih vezij z možnostjo zaporednega vezja; oba sta na voljo v kompaktnem 6-polnem ohišju SOT23. MAX16052 zagotavlja aktivni visok izhod z odprtim ponorom, medtem ko MAX16053 ponuja aktivni visok push-pull izhod. Oba zagotavljata nastavljiv nadzor napetosti za vhode do 0,5 V in izvajata nadzor napetosti z uporabo vhoda z visoko impedanco (IN) z interno fiksnim pragom 0,5 V.

Uporaba nadzornega časovnika

Nadzorni časovniki (WDT) lahko povečajo zaščitne zmogljivosti nadzornih vezij v primerih, ko je izhodni signal nizek, ko je izpolnjen pogoj za nadzor. V teh okoliščinah lahko nadzorni časovnik zazna pomanjkanje impulza ali prehod za določen čas, imenovan časovna omejitev nadzornika (tWD), in aktivira reset mikrokontrolerja ali sproži ciklično napajanje.

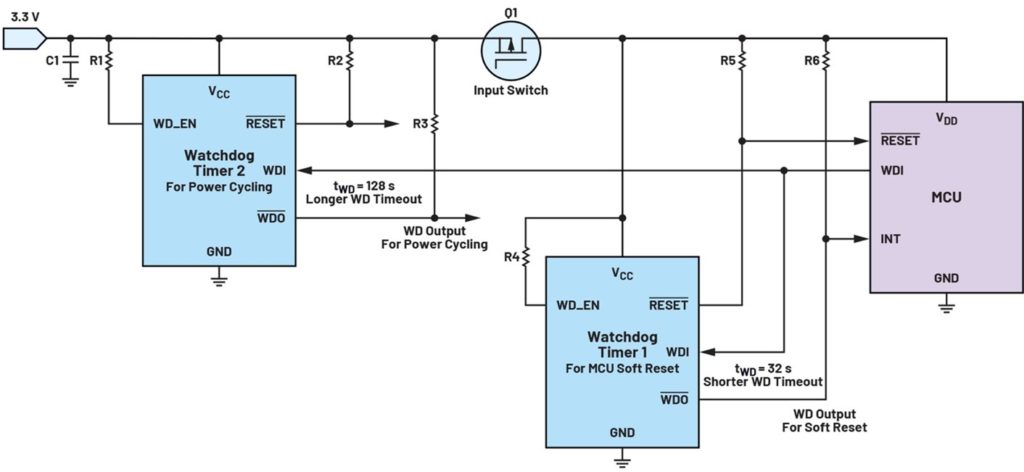

Nadzornik ADI MAX16155 nanoPower z nadzornim časovnikom sproži izhod za reset, ko pozitivna napajalna napetost (VCC) presega minimalno delovno napetost, čeprav je nižja od praga reseta. Aplikacija, ki uporablja dva WDT-ja (slika 3), lahko omogoči mehek reset mikrokontrolerja po 32 sek. nedejavnosti in ciklično napajanje sistema po 128 sek. nedejavnosti.

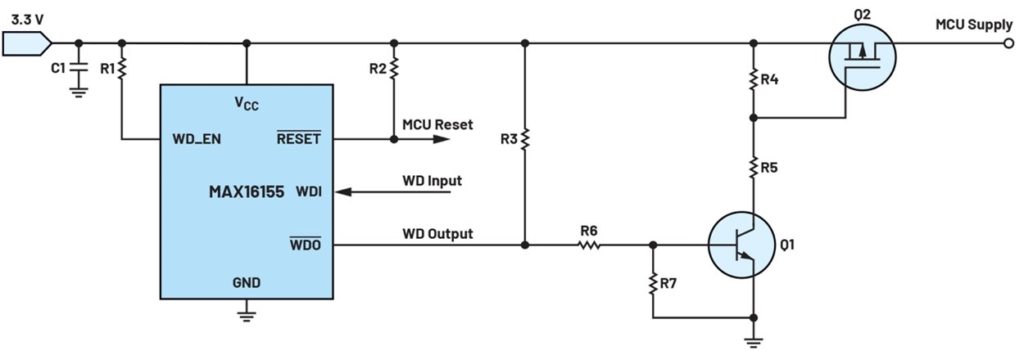

Ena od možnosti za poganjanje P-kanalnega stikala na visoki strani je uporaba bipolarnega spojnega tranzistorja NPN (BJT) kot pretvornika za pretvorbo nizkega signala izhoda nadzornika, ki izklopi tranzistor NPN, v visok signal, ki izklopi P-kanalni MOSFET prek pull-up upora. (Slika 4). Ko je sistem aktiven, je izhod nadzornika (WDO) visok in pošilja svoj signal skozi upor v bazo tranzistorja NPN in ga vklopi.

Uporovni delilnik, povezan z vrati MOSFET-a in virom, krmili VGS. Ko je tranzistor NPN vklopljen, potegne uporovni delilnik nizko, zaradi česar je napetost vrat nižja od napetosti vira, in vklopi P-kanalni MOSFET, da zagotovi napajanje sistema.

Če se mikrokontroler ne odziva ali ne pošlje vhodnih impulzov v vnaprej določenem obdobju časovne omejitve nadzornega časovnika MAX16155, pride do dogodka časovne omejitve nadzornika, zaradi česar WDO pin potrdi nizko stanje. To dejanje povleče bazo NPN na maso in jo izklopi. Ko je tranzistor NPN izklopljen, sta napetosti na vratih in viru P-kanalnega MOSFET-a enaki, kar izklopi MOSFET in prekine napajanje mikrokontrolerja.

Ko se izhod nadzornega časovnika WDO povrne na visoko raven, sistem nadaljuje z normalnim delovanjem. Mikrokontroler nato pošilja redne impulze na WDI pin, kar preprečuje nadaljnje časovne omejitve. Tranzistor NPN se vklopi, pri čemer ostane MOSFET na visoki strani vklopljen in zagotovi neprekinjeno napajanje mikrokontrolerja.

Nizki stroški bipolarnih spojnih tranzistorjev so konstrukcijska prednost za P-kanalna stikala na visoki strani, vendar zahtevajo ustrezno nastavitev s pomočjo dodatnih zunanjih komponent, kot so upori.

Krmilno vezje z uporabo N-kanalnega MOSFET-a

Uporaba N-kanalnega MOSFET-a za krmiljenje P-kanalnega MOSFET-a na visoki strani ima več prednosti pred bipolarnim tranzistorjem.

N-kanalni MOSFET ima nizek vklopni upor, kar zmanjša izgubo moči in poveča učinkovitost. Prav tako hitro preklaplja, kar izboljša odzivni čas sistema. Ima manjše izgube pri preklopu in lahko deluje pri višjih frekvencah, zaradi česar je idealen za energetsko učinkovite aplikacije, kot so naprave na baterije. Poleg tega so zahteve za pogon vrat manj zahtevne od zahtev za BJT, kar poenostavlja pogonsko vezje in zmanjšuje število komponent.

Izhod nadzornika lahko neposredno krmili vrata N-kanalnega MOSFET-a. Pull-up napetost WDO se mora ujemati z napetostjo praga vrat MOSFET (VGS(th)), da pravilno deluje. Ko je sistem aktiven, visok signal WDO vklopi N-kanalni MOSFET (Q1 na sliki 5), ki nato vklopi P-kanalni MOSFET (Q2 na sliki 5), ki napaja sistem. Med nedejavnostjo sistema nizek signal WDO izklopi Q1, ki izklopi Q2 in prekine napajanje.

Zaključek

Uporaba N-kanalnega ali P-kanalnega MOSFET-a za pogon stikala na visoki strani sta zanesljivi metodi za ciklično napajanje sistema.

P-kanalni pristop z bipolarnim tranzistorjem NPN in dodatnimi komponentami zagotavlja cenejše možnosti, medtem ko je dražji N-kanalni pristop boljši za visokofrekvenčno preklapljanje. Preference razvijalca in zahteve aplikacije narekujejo optimalen pristop.