Microchip Technology Inc.

Avtorja: Henrik Nyholm, Jacob Lunn Lassen

Praktični izzivi pri odkrivanju napak za SRAM (statični pomnilniki z naključnim dostopom) med izvajanjem z uporabo checkerboard algoritmov.

Pri načrtovanju varnostno kritičnih sistemov so mednarodni varnostni standardi ključnega pomena za izbiro ustreznih postopkov in ustreznih tehnik za odkrivanje in preprečevanje nevarnih napak v končnem izdelku. Standardi zagotavljajo, da ne pademo v iste pasti kot naši kolegi varnostni inženirji pred nami. Vendar pa je nevarnost standardov v tem, da predvidevajo podrobno poznavanje osnovne strojne opreme, na primer mikrokontrolerja, zaradi česar lahko manj izkušeni varnostni inženirji izvajajo nevarne projekte. Standard IEC (Mednarodna elektrotehniška komisija) 60730 na primer priporoča uporabo preizkusa pomnilnika s šahovnico za odkrivanje DC napak v spremenljivih pomnilnikih za programsko opremo razreda B, kar je bolj zahtevno, kot se morda zdi.

V tem članku je opisano, kako lahko zaradi nedokumentirane razlike med logično in fizično razporeditvijo SRAM pomnilnika nenamerno napačno izvedemo teste pomnilnika, kot je po principu šahovnice. Potrebne informacije običajno niso na voljo v podatkovni dokumentaciji standardnih mikrokontrolerjev, na srečo pa obstajajo algoritmi za testiranje pomnilnika, na katere razlika med logično in fizično razporeditvijo SRAM-a ne vpliva.

Zakaj testirati SRAM za napake med izvajanjem

Prodajalec integriranega vezja seveda testira SRAM pomnilnike v proizvodnji in izdelkov z napakami ne pošilja potrošnikom. Kljub temu pa se naključne napake v strojni opremi lahko pojavijo in se bodo pojavile med življenjsko dobo integriranega vezja, kar je eden od razlogov, da je treba v varnostno kritičnih aplikacijah preizkusiti strojno opremo v mikrokontrolerju v med delovanjem.

Preizkus spomina po principu šahovnice

Varnostni standardi, kot je IEC 60730 (H.2.19.6.1), predlagajo, da se lahko za prepoznavanje nekaterih napak (DC faults) v SRAM uporablja princip šahovnice za aplikacije, ki morajo ustrezati varnostni ravni razreda B. Preizkus kontrolne plošče se pogosto izbere, ker zajema najverjetnejše napake v SRAM-u in je razmeroma hiter, kar je primerno za zmanjšanje učinka na samo aplikacijo. Poleg DC napak, pri katerih je bit trajno blokiran visoko ali nizko, lahko princip šahovnice zazna tudi napake, pri katerih sosednji biti vplivajo drug na drugega.

SRAM je logično sestavljen iz števila bitov, organiziranih v besede. Besede so običajno široke 8, 16 ali 32 bitov, lahko pa so tudi daljše. Fizično so biti organizirani v polja, kjer ima vsak bit običajno osem sosednjih bitov (glej sliko 1). Fizična napaka v bitu lahko vpliva na en sam bit, tako da se ta postavi visoko ali nizko (DC napaka), lahko pa je napaka v ločitvi dveh bitov; v tem primeru lahko sosednja agresorska celica (na sliki 1 označena z vijolično) vpliva na celico žrtev (na sliki 1 označena z rumeno). Scenarij med agresorjem in žrtvijo se običajno imenuje napaka pri sklopitvi. Statistično gledano je verjetnost nastanka DC napake večja, vendar je še vedno pomembno zaznati najverjetnejše napake sklopitve.

Če napaka vpliva na en sam bit, tako da je bit blokiran visoko ali nizko, jo lahko razkrijemo tako, da zapišemo vrednost ena, preverimo enico s ponovnim branjem, nato pa zapišemo vrednost nič in preverimo ničlo s ponovnim branjem, kot je prikazano na sliki. Če pa gre za sklopitveno napako med dvema sosednjima bitoma, na primer bitoma stolpca 9 in 10 v vrstici 2, določeni vzorci, kot so vse enice ali vse ničle, ne bodo razkrili sklopitvene napake, saj imajo celice med preskusom enako vrednost.

Takšne sklopitvene napake, kot so sosednje celice (na straneh, zgoraj in spodaj), imajo nasprotne binarne vrednosti. (spodaj desno) prikazuje, da je enica v bitu 10 kontaminirala bit 9, in sklopitvena napaka se razkrije, saj bit 9 nima pričakovane vrednosti, nič.

Fizična proti logični razporeditvi SRAM-a

Za delovanje algoritma šahovnice je treba vedeti, kateri biti so sosednji biti. To se izkaže za težavo, saj podatkovni listi običajno opisujejo le logično razporeditev SRAM-a, ne pa tudi, kako je SRAM fizično organiziran.

Za razumevanje fizične postavitve SRAM pomnilnika je treba razlikovati med bitno usmerjenimi pomnilniki (BOM), pri katerih je mogoče dostopati do enega bita hkrati, in besedno usmerjenimi pomnilniki (WOM), pri katerih se hkrati bere in piše n-bitna beseda. Medtem ko je večina pomnilnikov v resničnem svetu izvedena kot WOM, klasični algoritmi za testiranje pomnilnika v znanstveni literaturi pogosto predpostavljajo izvedbe BOM.

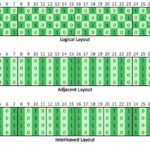

Pri WOM pomnilnikih obstajajo tri glavne kategorije fizične organizacije bitov, ki sestavljajo besedo: sosednji, prepleteni in podpolja. Medtem ko je pri logični razporeditvi vsaka beseda postavljena pod prejšnjo besedo v istem stolpcu (podobno naslovnemu prostoru), je pri sosednjih pomnilnikih vsaka beseda postavljena v isto vrstico druga poleg druge, kot je prikazano na sliki 2. Prepletene arhitekture ločijo vsak bit besede v različne stolpce in vrstice polja SRAM. Nazadnje, organizacija s podpoljem postavi vsak bit besede v različne fizično ločene bloke SRAM-a. V resnici fizične razporeditve, ki je potrebna za pravilno izvedbo testa šahovnice, ne poznate.

Lastnosti in pomanjkljivosti testa po principu šahovnice

Domnevno enostaven pristop za izvajanje algoritma šahovnice je izmenično zapisovanje vrednosti 0xAA (ob predpostavki 8-bitnih podatkovnih besed) na prvi naslov in 0x55 na naslednji naslov, dokler se vsi naslovi, ki se testirajo, ne zapolnijo s šahovnico enic in ničel. Vzorec se nato preveri, da se odkrijejo morebitne napake pri enosmerni napetosti ali sklopitvi med sosednjimi celicami. Postopek se nato ponovi z uporabo obratnega vzorca. Kot je bilo že navedeno, je tu še ena past: vzorec šahovnice v logični postavitvi pomnilnika ni nujno enak vzorcu šahovnice v osnovni fizični postavitvi.

Izravnava razlike med logično in fizično postavitvijo se zdi samoumevna, vendar so potrebne informacije le redko na voljo v podatkovnem listu naprave. Kaj torej storiti? Sprejeti manjšo pokritost, navsezadnje bo diagnostika še vedno zajela napake enosmerne napetosti in nekatere napake sklopitve med sosednjimi biti? Od prodajalca integriranega vezja zahtevati postavitev in za vsako napravo po meri izvesti test šahovnice? Ali izbrati drug algoritem?

Zdaj, ko ste seznanjeni z morebitnimi pomanjkljivostmi testa s šahovnico, se lahko odločite na podlagi informacij.

Alternativni algoritmi za testiranje SRAM-a med izvajanjem

Tehnike testiranja pomnilnika, predlagane v IEC 60730 za varnostno raven razreda C, imajo večjo pokritost odkrivanja napak, vendar ti algoritmi spadajo med algoritme, ki jih lahko štejemo za proizvodne testne algoritme: trajajo dlje časa, odkrivajo tudi redkejše vrste napak, vendar običajno uničijo podatke, shranjene v SRAM, saj delujejo na celotnem SRAM in ne v podblokih. Na splošno tega pri našem ugnezdenem razvoju ne prenašamo najbolje. Zato predlagamo, da razmislite o hibridnih March algoritmih, prilagojenih iz testnega produkcijskega March algoritma: ti algoritmi so na voljo v optimiziranih izvedbah WOM in zagotavljajo visoko testno pokritost. Poleg tega se lahko ti hibridni March algoritmi izvedejo tako, da se izvajajo na manjših prekrivajočih se delih SRAM-a, da se prepreči brisanje vseh podatkov v SRAM-u naenkrat, kar pomeni, da se je mogoče izogniti ponovnemu zagonu ugnezdenega sistema. Pomanjkljivost March algoritmov je, da so računsko zahtevnejši od tradicionalnih algoritmov šahovnice, vendar je to cena, ki je lahko potrebna v varnostno kritičnih sistemih.

Če razmišljate o zamenjavi tradicionalnega testa s šahovnico z March testom, lahko takšno izvedbo najdete pri nekaterih prodajalcih mikrokontrolerjev. Microchip je eno od podjetij, ki v okviru svojih programskih diagnostičnih knjižnic ponuja zmogljivostno optimizirano implementacijo March algoritma v C jeziku. Microchip podpira testiranje celotnega pomnilnika SRAM, ki se običajno izvede le ob zagonu, da se doseže največja pokritost s testi, in tudi testiranje manjših pomnilniških blokov, namenjeno zmanjšanju vpliva na aplikacijo v realnem času. Izvedbo je mogoče brezplačno prenesti s spletne strani podjetja Microchip [1] kot del knjižnice IEC 60730 razreda B. Izvedba je namenjena PIC® in AVR® mikrokontrolerjem, vendar jo je mogoče prenesti na druge Microchip mikrokontrolerje.

Za več informacij o preskusih IEC 60730 razreda B preverite [2].

O avtorjih

Henrik Nyholm: odgovoren za razvoj izdelkov in programske opreme za varnostno kritične sisteme v skladu z ISO 26262 in IEC 60730.

LinkedIn: [3]

Jacob Lunn Lassen: vodja tehničnega poslovnega razvoja za varnostno kritične sisteme, odgovoren za tržno strategijo in projekte, usmerjene v standarde ISO 26262, IEC 61508 in IEC 60730 z Microchipovimi mikrokontrolerji serij PIC in AVR.

LinkedIn: [4]

Viri:

1: https://www.microchip.com/PIC-AVR-IEC60730

2: https://www.microchip.com/PIC-AVR-IEC60730

3: https://www.linkedin.com/in/henrik-nyholm-877a07224

4: https://www.linkedin.com/in/jacob-lunn-lassen-560b0b3/

Opomba: Ime in logotip Microchip sta registrirani blagovni znamki podjetja Microchip Technology Incorporated v ZDA in drugih državah. Vse druge blagovne znamke, ki so morda tu omenjene, so last njihovih podjetij.