Če smo se v SE311 spraševali, kateri mikrokontroler je najprimernejši za naše potrebe, se bomo tokrat podrobneje lotili ključnih novosti v svetu 8-bitnih PIC in AVR mikrokontrolerjev, s katerimi lahko zmanjšamo kompleksnost tiskanih vezij in obenem pohitrimo njihovo delovanje.

Avtor: dr. Simon Vavpotič

Navadno smo članek o Microchipovih mikrokontrolerjih začeli s PIC16 in PIC18, a tokrat začnimo z s pomembnima družinama AVR, ki dozdevno prinašata največ tehnoloških novosti na področju 8-bitnih mikrokontrolerjev. Vsekakor pa ni bojazni, da bi se prodor novih tehnologij v 8-bitne družine PIC in AVR ter izmenjava tehnoloških rešitev med njimi zaustavila. Vseeno pa ne bomo podrobno opisovali starih in dobro znanih funkcionalnosti, o katerih ste že lahko brali preteklih letnikih Sveta elektronike.

Ta vsebina je samo za naročnike

Mikrokontrolerski družini AVR DA in AVR DB

Novi AVR-jevi družini prinašata kopico novosti in sta certificirani za vgradnjo v aplikacije, pri katerih je kritična varnost delovanja. V mikrokontrolerje obeh družin so ugnezdene številne napredne funkcijske enote, ki jih lahko razdelimo v 6 skupin: (1) merjenje časa, merjenje in nadzor oblike signalov, (2) komunikacije, (3) ugnezdene analogne enote, denimo operacijski ojačevalniki, A/D in D/A pretvorniki in primerjalniki napetosti, (4) nadzor in varnost, (5) logične in matematične funkcije in (6) funkcije za prilagodljivost.

AVR DB se od družine AVR DA, se razlikuje predvsem po tem, da je namenjena prilagajanju signalov (angl. signal conditioning), medtem je pri AVR DA poudarek na krmilnih funkcionalnostih, denimo funkcionalnosti za izvedbo zaznavanja dotika. Mikrokontrolerji obeh novih družin si sicer delijo tudi 24 MHz AVR procesorsko jedro, do 128 kB flash RAM-a, do 16 kB SDRAM-a in do 512 bajtov podatkovnega EEPROM-a.

Čipi imajo 28, 32, 48 ali 64 priključkov, pri čemer je število priključkov odvisno tudi od velikosti in izvedbe čipa. Za ročno spajkanje in domače projekte je morda še najprimernejše ohišje SPDIP z 28 priključki, medtem, ko so ostali čipi v SMD ohišjih, od katerih je za ročno spajkanje primerno le ohišje SOIC s prav tako 28 priključki.

Dinamično prilagajanje napetostnih nivojev

Ko so 5-voltne mikrokontrolerje pred že pred vrsto leti začeli nadomeščati 3,3-voltni, so pri Microchipu v nekatere do slednjih (npr. v 8-bitno družino PIC18FxxJyy in 32-bitno družino PIC32MX) vgradili nekaj na 5,5 V tolerantnih vhodov, ki jih lahko neposredno povežemo s 5-voltnimi napravami. Pri tem so izhodni priključki 3,3-voltnega mikrokontrolerja dizajnirani tako, da visoko staje (logična 1) zanesljivo zazna tudi 5-voltna logika.

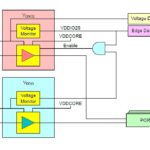

Vendar gre MVIO tehnologija še korak dlje. Z uporabo dveh napajalnih priključkov, enega za napajanje mikrokontrolerja in drugega za napajanje napetostnega pretvornika, se lahko napetostni nivo MVIO priključkov sproti prilagaja nihanju napajalne napetosti zunanje naprave, oziroma drugim potrebam. Obenem pri nadaljnjem zniževanju delovne napetosti na vsega 1,8 V (npr. pri najnovejših mikrokontrolerjih z visokim delovnim taktom – več 100 MHz) enostavno prilagajanje napetostnih nivojev ni več mogoče; tako sta edini možnosti uporaba v mikrokontroler ugnezdenega prilagoditvenega vezja ali uporaba zunanjega prilagoditvenega vezja. AVR DB je zaenkrat edina med vsemi PIC in AVR mikrokontrolerskimi družinami, ki ima tehnologijo MVIO. Več o delovanju MVIO ste lahko prebrali v Microchipovem članku, Odprava pretvornikov nivojev v mikrokontrolerskih aplikacijah, v SE310 in SE311. Tokrat pa skušamo novo tehnologijo celostno umestiti v svet Microchipovih mikrokontrolerjev z njenimi prednostmi in slabostmi, zato v nadaljevanju še nekaj praktičnih izkušenj.

MIVO v praksi

Ko natančno pregledamo podatkovni list nove AVR DB mikrokontrolerske družine, opazimo da so mogoči napetostni režimi delovanj posameznih priključkov označeni z barvami. V tem pogledu so še posebej zanimivi tisti, ki so označeni z modro in rumeno barvo, saj edino ti podpirajo tehnologijo MVIO. Njihovo število (od le 4 pri čipih z 28 priključki in največ 8 pri čipih s 64 priključki) je podobno kot število na 5,5 V odpornih priključkov pri družinah PIC18FxxJyy in PIC32MX. Zato je več kot očitno, da lahko prilagoditev napetostnih nivojev v praksi uporabimo predvsem za serijske komunikacije s protokoli, kot so: SPI, I2C, RS-232 idr.

Ima pa MVIO pred klasičnimi načini prilagajanja napetostnih nivojev, denimo z uporovnimi delilniki, Zener diodami in upori, tranzistorji in upori itn., pomembno prednost, saj lahko višino referenčne napetosti (VDDIO2) napetostnega pretvornika med delovanjem mikrokontrolerja hitro spreminjamo, denimo s pomočjo v AVR DB mikrokontroler vgrajenega D/A pretvornika, katerega izhod povežemo z vhodom enega izmed treh ugnezdenih operacijskih ojačevalnikov. Tako ustvarimo napetostno moduliran digitalni signal, katerega vrhnja vrednost niha v ritmu signala iz operacijskega ojačevalnika, s katerim dinamično spreminjamo vrednost napetosti na priključku VDDIO2. Povejmo še, da lahko napetost VDDIO2 izberemo ne glede na napajalno napetost mikrokontrolerja VDD. Dovoljena vrednost vsake od omenjenih napetosti je med 1,8 V in 5,5 V.

CRC/SCAN za PIC in AVR mikrokontrolerje

Zaradi številnih načinov, kako posodobiti ugnezdeno programsko opremo med delovanjem mikrokontrolerja, ki jih uporabljajo proizvajalci ugnezdene programske opreme, slednja nemalokrat ni najbolj varna pred hekerji. Ena izmed rešitev je izračun CRC kontrolne kode in njen vpis v poseben register CRC/SCAN ugnezdene enote mikrokontrolerja, ki pred njegovim zagonom vsakokrat preveri skladnost shranjene CRC kode z izračunano na osnovi trenutne vsebine Flash RAM pomnilnika. Če se razlikujeta, zagona mikrokontrolerja ne dovoli. CRC/SCAN funkcije imajo vgrajene tako novejši 8-bitni AVR kot tudi novejši 8-bitni PIC mikrokontrolerji.

Programirljive CLC logične celice

Medtem, ko je masovna FPGA logika ključ do uspeha najnaprednejših Microchipovih PolarFire mikrokontrolerjev, so tehnologijo v veliko manjšem obsegu, zgolj nekaj logičnih funkcij, vgradili tudi novejše PIC in AVR. Prednost implementacije različnih logičnih funkcij neposredno v strojni opremi, še posebej znotraj mikrokontrolerja, je bistvena pohitritev in avtomatizacija delovanja komunikacijskih protokolov. Logične funkcije se izvajajo ne glede na stanje procesorskega jedra mikrokontrolerja, pogosto celo med spanjem mikrokontrolerja.

V nove 8-bitne PIC mikrokontrolerje je vgrajena t.i. tehnologija nastavljivih logičnih celic CLC (angl. configurable logic cells), v 8-bitne AVR mikrokontrolerje pa t.i. tehnologija uporabniško nastavljive logike CCL (angl. configurable custom logic). Gre za zelo podobni tehnologiji, ki izhajata iz FPGA vezi s tisočerimi medsebojno povezljivimi logičnimi elementi z nastavljivo logično funkcijo.

No, pri mikrokontrolerjih, kot je PIC16F18855, ki ga dobimo na XPress razvojni ploščici imamo na voljo štiri CLC module. Vsak lahko deluje kot logično vezje s štirimi vhodi: AND, NAND, AND-OR, AND-OR-INVERT, OR-XOR, OR-XNOR in pomnilne celice: S-R (set-reset) flip-flop, D-pomnilna celica s taktnim signalom, D-pomnilna celica s signaloma set (S) in reset (R) in s taktnim signalom sinhroniziran J-K flip-flop z reset signalom.

Na krmilne vhode CLC modulov lahko preko, v mikrokontroler vgrajenih multiplekserjev, povežemo priključke mikrokontrolerja, njegove notranje taktne signale, izhode ugnezdenih perifernih enot ali vrednosti bitov posebnih registrov pa tudi izhodne vrednosti drugih CLC modulov. Za vsak vhod v logična vrata lahko uporabimo 48 različnih virov vhodnih signalov, med katerimi so tudi prekinitveni signali. Vir vsakega od vhodov izbiramo s spodnjimi šestimi biti posebnega 8-bitnega registra, pri čemer so dovoljene vrednosti le med 0 in 47. Priključke na ohišju čipa kot vhode izbiramo posredno prek PPS enote (angl. Peripheral pin select unit), vendar moramo pri tem upoštevati tudi določene omejitve, ki so podane v podatkovni poli izbranega mikrokontrolerja.

CLC modul lahko sproži tudi prekinitev, ko se spremeni njegove izhodna vrednost iz 0 v 1 (prednja fronta) ali iz 1 v 0 (zadnja fronta). Še posebej zanima možnost je uporaba CLC modulov v kombinaciji z drugimi funkcijskimi enotami, kot so časovniki, napetostni primerjalniki pa tudi EUSART, ki omogoča različne vrste serijske komunikacije. Z uporabo CLC modulov lahko strojno podpremo razširjene različice komunikacijskih protokolov, ki omogočajo večji nadzor in obenem večjo zanesljivost prenosa podatkov.

Povezava CLC modulov s časovniki in napetostnimi primerjalniki omogoča zanesljivejše in natančnejše merjenje analognih signalov, saj lahko izdelamo primerjalnik, ki hkrati spremlja vrednosti več signalov in sproži prekinitveni program za njihovo obdelavo šele, ko dosežejo vhodni signali želene vrednosti.

Na primer, če želimo z A/D pretvornikom zajeti signal od prednje fronte naprej, ob dodatnem pogoju, da ima nek drugi analogni signal točno določeno vrednost napetosti, lahko s pomočjo CLC modula logično povežemo dva primerjalnika napetosti in A/D pretvornik. Slednji začne vzorčiti, ko je pri obeh napetostnih primerjalnikih izpolnjen zahtevan pogoj. Ob izpolnitvi pogojev izhod CLC modula preide iz 0 v 1, ob čemer CLC modul sproži prekinitev A/D pretvornika, ki zažene vzorčenje signala.

Delovanje CLC modulov je sicer neodvisno od delovanja sistemske ure mikrokontrolerja, zato delujejo tudi, ko je mikrokontroler v stanju spanja, vendar pod pogojem, da pri tem delujejo tudi viri vhodnih signalov.

Z uporabo CLC logičnih vrat v mikrokontrolerju se izognemo tudi potrebi po dodajanju enostavnih logičnih vezij.

CLC moduli, Microchip Xpress Development Board in MPLAB Xpress IDE

MPLAB X je odlično razvojno okolje, ki ga lahko namestimo v svoj računalnik, ali pa namesto tega uporabimo Microchip MPLAB Xpress Cloud-based IDE spletno razvojno okolje (MPLABXpress.microchip.com), katerega lahko po brezplačni prijavi uporabljamo kar s pomočjo novejšega spletnega brskalnika, denimo Google Chrome. Izgled okolja je skoraj popolnima enak kot MPLAB X IDE, ki ga namestimo v osebni računalnik, le da nam Xpress okolja ni potrebno nameščati in posodabljati, hkrati pa prevajanje programske kode poteka relativno hitro.

Moram priznati, da sem bil glede slednjega pozitivno presenečen, saj je dostop do MPLAB Xpress Cloud-based IDE mogoč iz skoraj kateregakoli pametnega telefona, vsekakor pa tudi iz Raspberry Pi 4, ki sem ga uporabil skupaj z razvojno ploščico Microchip Xpress Development Board pri testiranju CLC funkcionalnosti. Prevajanje izvorne programske kode je v mojem primeru teklo gladko, prav tako njen programiranje v PIC16F18855, za katerega poskrbi na razvojni ploščico vgrajeni programator.

Slednji se PC-ju predstavi kot dodatni podatkovni pogon, na katerega preprosto odložimo datoteki *.HEX s prevedeno strojno kodo za PIC16F18855 mikrokontroler. Za samodejno programiranje in ponovni zagon mikrokontrolerja nato poskrbi programator. Za slednjega so pri Microchipu uporabili 8-bitni PIC18LF25K50, ki se s PC-jem poveže prek USB vodila in se predstavi kot kombinirana naprava s podatkovnim pogonom in zaporednimi vrati (COM).

Prek slednjih lahko, podobno kot pri Arduino projektih, izpisujemo statusna sporočila med delovanjem aplikacije. Res pa je, da PIC18LF25K50 ne omogoča razhroščevanja programske kode, za kar potrebujemo zunanji programator, denimo PICkit 4, ki ga povežemo na priključek J4 s spodnje strani razvojne ploščice. Nerodno je le, ker so kontakti zgolj na eno strani ploščice in nimajo skoznikov. Zato lahko nanje prispajkamo SMD konektor. Če pa se odločite prispajkati kabel, pazite da priključkov ne odtrgate, ali pri spajkanju poškodujete drugih delov tiskanine. Povejmo še, da tudi MPLAB X IDE v6.0 ob nameščenem najnovejšem XC8 C/C++ prevajalniku nima težav s prevajanjem programske kode za PIC16F18855, nekoliko se je treba potruditi le za vzpostavitve delovanja Microchip Code Configuratorja (MCC).

Razvoj CLC podprtih aplikacij v praksi

Z uporabo CLC modulov lahko učinkovito rešimo različne probleme, za katere bi sicer potrebovali precej zmogljivejši mikrokontroler, morda celo takega z več procesorskimi jedri. Denimo, veliko med samograditelji priljubljenih Espressif Systems ESP32 modulov ima po dve procesorski jedri, od katerih pri zahtevnejših aplikacijah eno pogosto namenimo periodičnemu preverjanju pripravljenosti zunanjih naprav na prenos podatkov. Vendar je energijsko neprimerno bolj varčno, če lahko za taka preverjanja uporabimo strojno logiko, še posebej tisto, ki je že vgrajena v mikrokontroler.

Razvoja programske kode se lahko lotimo neposredno z vpisovanjem vrednosti v nastavitvene registre vsakega od CLC modulov, ali pa namesto tega uporabimo grafično načrtovalsko orodje, ki je del MCC. V grafiki izbiramo vezavo vhodnih signalov na vsakega od štirih vhodov logičnega vezja, kakor tudi vklapljamo ali izklapljamo negacijo vsakega od signalov, kar nam omogoča tvorjenje zelo raznolikih logičnih funkcij. Dodatno lahko izberemo tudi že omenjeni tip logičnega vezja, ki ga nato vidimo tudi v grafični predstavitvi. Pri načrtovanju zaresnih aplikacij na tem mestu vsekakor pride še kako prav tudi znanje iz optimizacije logičnih vezi in poznavanje pretvorb med logičnimi izrazi, ki jih izvajamo s posamezno konfiguracijo CLC modula.

Denimo logični izraz NOT(NOT(X) OR NOT(Y)) ustreza izrazu X AND Y, kjer sta X in Y 1-bitni binarni vrednosti. Slednje lahko vselej preverimo tudi z resničnostno tabelo, v katero vnesemo 4-mogoče vhodne kombinacije vrednosti signalov X in Y (t.j. 00, 01, 10 in 11).

Je pa res, da načrtovanje tovrstnih enostavnih logičnih funkcij za povprečnega programerja danes ni več nekaj povsem običajnega, saj je v dobi mikrokontrolerjev marsikdo prepričan, da se da vsak problem rešiti le z dovolj dovršeno programsko kodo, ki jo izvaja dovolj hitro procesorsko jedro. Načrtovanje s aplikacij s pomočjo CLC modulov in veliko zahtevnejših FPGA vezji je v tem pogledu korak nazaj h koreninam računalništva. Je pa res, da imamo za FPGA vezja na voljo veliko zmogljivejša razvojna orodja, ki že vsebujejo šablone za tvorbo registrov, števcev, časovnikov in drugih kompleksnih logičnih elementov, ki jih potrebujemo za gradnjo zmogljivih funkcijskih enot s poljubno funkcionalnostjo.

Primer: CLC 4-bitna enota zxa serijsko komunikacijo

Čeprav EUSART enota podpira popularne serijske komunikacijske protokole, lahko s CLC moduli v omejenem obsegu podpremo tudi lastne protokole, med drugim tudi take, ki jih EUSART enota ne podpira. Pri tem igra register CLCDATA register še posebej pomembno vlogo, saj omogoča hkratno branje izhodov vseh štirih CLC modulov z enim samim strojnim ukazom. To je podobno kot pri EUSART enoti, kjer vsak sprejeti bajt preberemo hkrati.

Poskusimo implementirani protokol za prenos štirih bitov podatkov po dveh podatkovnih vodnikih. Oddajni računalnik bo prisotnost prve dvojice bitov označil z logično vrednostjo signala S = 0 in prehodom taktnega signala C iz 0 v 1. Logično vezje iz štirih CLC modulov mora zajeti spodnja 2 bita podatkov in jih shraniti v D-pomnilni celici 0 in 1. Sledi nov cikel prenosa podatkov, ko bo vrednost signala S ob prehodu taktnega signala C in 0 v 1 enaka 1. Logično vezje mora zajeta bita shraniti v D-pomnilni celici 2 in 3.

Ko imamo izdelan koncept, se lahko lotimo izdelave logičnega vezja. PIC16F18855 ima kar nekaj prostih splošno-namenskih vhodno-izhodnih priključkov, zato ni težko izbrati štirih, ki jih bomo povezali CLC modulu. Uporabili bomo 4 povezave: 2 podatkovni, D0 in D1, C – taktni signal, ki ga ustvari računalnik in S – signal za označitev začetka komunikacije. Slednja ustvari oddajni računalnik.

Če se konfiguracije CLC modulov lotimo v MCC velja opozorilo, da moramo vsak modul najprej iz Device Resources z dvoklikom dodati v Project Resources, ga odpreti in omogočiti (v meniju zavihka Easy Setup damo kljukico pod Enable CLC), šele nato lahko na desni stran s klikom na priključek na sliki čipa PIC16F18855 izberemo priključek, ki ga bomo priredili enemu od štirih zunanjih vhodov v CLC modul. Je pa tudi res, da se pred določanjem zunanjih priključkov splača izbrati tip modula. Sam sem izbral eno-vhodno D-pomnilno celico s taktnim signalom in signaloma set (S) in reset (R). Nato sem za podatkovna signala izbral RA7 (vezan na CLCIN1) in RA6 (vezan na CLCIN0). S tem je RA6 postal podatkovni bit 0, RA7 pa podatkovni bit 1. Za taktni signal sem uporabil RB6 (vezan na CLCIN2). Za S-signal CLCIN3 pomnilnih celic sem uporabil PB7 (vezan na CLCIN3).

Naslednji korak so povezave: CLCIN0 na D vhod D-pomnilniške celice 1, izhod pomnilniške celice 1 (CLC1OUT) na D vhod D-pomnilniške celice 3, vhoda CLCIN1 na D vhod D-pomnilniške celice 2 in izhod pomnilniške celice 2 (CLC2OUT) na D vhod D pomnilniške celice 4. Zdaj je treba povezati še taktni signal, ki ga pripeljemo prek vhoda CLCIN2 na CLK vhode vseh D-pomnilniških celic. Podobno S-signal iz vhode CLCIN3 povežemo na vse R vhode D-pomnilniških celic.

Delovanje vezja je enostavno, saj oddajni računalnik pred prenosom podatkov sproži impulz preko signalnega voda S, s katerim izbriše vse vsebine D-pomnilniških celic hkrati. Nato postavi prva dva bita na podatkovno vodilo in odda taktni impulz, s katerim se podatka preneseta v pomnilniški celici 1 in 3. V naslednjem koraku omenjeno ponovi, vendar se pri tem hkrati obstoječa vsebina iz pomnilniških celic 1 in 3 prenese v pomnilniški celici 2 in 4, v pomnilniški celici 1 in 3 pa se prenese nova vsebina iz vodila. Tako je 4-bitni podatek pripravljen za branje in PIC16F18855 mikrokontroler ga lahko prebere iz registra CLCDATA z enim strojnim ukazom.

Povejmo še, da so neuporabljeni vhodi v CLC module vezani na maso, oziroma imajo logično vrednost nič. Vsaka 4-vhodna logična vrata OR (glej sliko) so vezana na enega od vhodov izbranega logičnega vezja (AND vrata ali flip-flop). Če hočemo na vhodu stalno logično enico, nastavimo vse 4 OR logičnih vrat na vrednost 0 in na izhodu OR izberemo negacijo.

Po vsem napisanem lahko hitro ugotovimo, da nam CLC daje obilico možnosti za realizacijo enostavnejših logičnih vezij, ki so nepogrešljiva pri hitrih predobdelavah podatkov. Poglejmo še, kako podobno CLC tehnologijo uporabljamo pri AVR mikrokontrolerjih.

Nastavljiva uporabniška logika AVR

Pri AVR mikrokontrolerjih imamo namesto CLC tehnologije CCL tehnologijo (angl. Configurable Custom Logic), katere delovanje je podobno. AVR CCL temelji na LUT (vpoglednih tabelah), katerih izhod je vezan na t.i. zaporednik. Za slednjega lahko izberemo sinhrono D-pomnilno celico s taktnim vhodom, asinhrono D-pomnilno celico z vrati, J-K fip-flop in S-R flip-flop. S pomočjo LUT tabel zbiramo vhodne signale in implementiramo logične funkcije. Pri tem sta na izhodu vsake LUT na voljo tudi digitalni filter in detektor prehoda signala iz nizkega v visok logični nivo in obratno. S filtrom izločimo prehodne pojave, denimo nihanja toka ob pritisku na električno stikalo. Po drugi strani detektor prehoda zazna spremembo stanja signala in lahko sproži vhod logičnega vezja, denimo vhod S S-R flip-flop. Kakorkoli, odkar je mogoče AVR in PIC mikrokontrolerje programirati v MPLAB X okolju, lahko trdimo, da za programerja, ki je po novem hkrati tudi načrtovalec enostavnih logičnih vezij, ni kakih posebnih razlik. Zato ostane predvsem vprašanje, kako se lotiti novega razvojnega projekta z 8-bitnim mikrokontrolerjem, da čimbolj izkoristimo njegove zmogljivosti in se hkrati izognemo potrebi po kompleksnejših 32-bitnih mikrokontrolerjih.

Kako začeti?

Vsekakor moramo najprej natančno vedeti, kakšen problem želimo rešiti. Če bomo 8-bitni mikrokontroler za zajem in predobdelavo podatkov iz analognega tipala, so ključna tri področja: zajem podatkov iz tipala (navadno analognega), preoblikovanje podatkov v obliko, ki jo je po zaporednem vodilu SPI, I2C ipd. enostavno prenesti v zmogljivejši 32-bitni mikrokontroler, ki predstavlja srce digitalne naprave, in zagotovitev zanesljivega prenosa podatkov, s katerim čim manj obremenimo v 32-bitnem mikrokontrolerju ugnezdeno eno- ali večjedrno procesno enoto.

Naslednji korak je načrtovanje mikrokontrolerske naprave, pri katerem navadno najprej začrtamo osnovni dizajn strojne opreme, katere del bomo implementirali tudi v CLC ali CCL logiki, šele nato pa se lotimo razvoja ugnezdene programske opreme. Povejmo še, da imajo napredni načrtovalci tudi možnost dinamičnega spreminjanja arhitekture CLC ali CCL vezja, tako je mogoče (vendar ne naenkrat) realizirati različna logična vezja. MCC grafiki lahko sicer načrtamo zgolj eno vezje, ki se naloži ob zagonu mikrokontrolerja, vendar pa lahko z MCC izdelane konfiguracijske datoteke shranimo, spremenimo dizajni in nato dodatno integriramo prej izdelani dizajn vezja. Potem lahko programsko preklapljamo med obema dizajnoma.

Prihodnjič

V naslednjem nadaljevanju nadaljujemo s posebnimi funkcionalnostmi novih mikrokontrolerskih družin, ki pomembno vplivajo na njihovo zmogljivosti v primerjavi s starimi družinami. Dodatne strojne funkcionalnosti in enako procesorsko jedro dajejo omogočajo razvoj novih naprav, ne da bi morali bistveno spremeniti že optimizirane in preizkušene ugnezdene programske opreme, za katerimi so lahko tudi leta razvoja in načrtovanja. Vsekakor tu nimamo v mislih domačih projektov, pri katerih si samograditelji z boljšim in malce dražjim mikrokontrolerjem pogosto »dajo krila«, ampak velikoserijske aplikacije, pri katerih si proizvajalci ne morejo privoščiti napak.