Razvijalci satelitskih sistemov in vesoljskih plovil imajo pri izbiri polprevodnikov s programirljivimi vrati (FPGA) kar nekaj različnih možnosti. Ena od FPGA možnosti so komercialne komponente (COTS), ki zmanjšujejo stroške na enoto komponent in čas izdelave, vendar na splošno niso dovolj zanesljive, zato jih je treba nadgraditi (kar poveča stroške in inženirske vire) ter zahtevajo mehko in trdo Trojno modularno redundanco (TMR) za ublažitev učinkov sevanja v vesolju.

Microchip Technology Inc.

Avtor: Julian Di Matteo

2022-307-15

V misijah, kjer napaka ni dovoljena, razvojniki običajno izberejo dražje FPGA-je, ki so zaradi zasnove utrjeniproti sevanju (RHBD), so že pregledani in kvalificirani za standarde Q in V razreda seznama kvalificiranih proizvajalcev (QML). QML razred V je najvišji standard kvalifikacij za vesoljske polprevodnike. Misije s posadko in varnostno kritične misije se zanašajo na QML-V komponente, da se zmanjša tveganje okvare.

Sistemi morajo izpolnjevati vedno večjo potrebo po zahtevni kombinaciji višje zmogljivosti in večje obdelave podatkov v napravi ter zmogljivosti visoke hitrosti komunikacije v vesolju. Ti RT FPGA, odporni na sevanje, zagotavljajo rešitev, ki je po zasnovi odporna na sevanje, podprta z dediščino in strokovnim znanjem proizvajalca o vesoljskih poletih ter z rešitvami, ki so podvržene QML testiranju razreda V. Ta članek bo obravnaval različne FPGA tehnologije, ki so na voljo za vesoljske aplikacije, in postopek za razvoj komponent.

Učinki sevanja v vesolju

RT FPGA so potrebni, ker COTS komponente niso imune na različne učinke sevanja v vesolju in lahko poslabšajo zmogljivost integriranega vezja ali povzročijo njegovo odpoved.

Eden od teh učinkov sevanja je celotna ionizirajoča doza (angl. total ionizing dose, TID), ki jo povzroči sevanje zaradi nabitih delcev in gama žarkov v vesolju. To sevanje odlaga energijo tako, da povzroči ionizacijo v materialu. Ionizacija lahko spremeni lastnosti vzbujanja naboja, prenosa naboja, vezave in razgradnje materiala.

To negativno vpliva na parametre naprave. TID je kumulativno ionizirajoče sevanje, ki ga prejme elektronska naprava v določenem obdobju, običajno v času misije. Škoda je odvisna od količine sevanja in je izražena v absorbirani dozi sevanja (angl. radiation absorbed dose, RAD). Glede na toleranco sevanja za TID lahko naprava doživi funkcionalne ali parametrične okvare. Med pogostimi parametri, na katere vpliva TID sevanje v FPGA, je povečanje zakasnitve širjenja, ki zmanjša zmogljivost naprave. Drug mehanizem okvare je povečanje slepega toka po visoki TID izpostavljenosti.

Druga vrsta učinka sevanja so učinki posameznega dogodka (angl. single-event effects, SEE). To so trenutne motnje, prehodi ali trajne poškodbe zaradi sevanja delcev, kot so protoni, težki ioni in alfa delci, ki lahko udarijo v občutljiva področja tranzistorja in povzročijo različne okvare. SEE se pojavljajo v različnih oblikah, vključno z motnjami posameznega dogodka (SEU), ki se pojavijo, ko visokoenergetski ionizirajoči delci, kot so težki ioni, delci alfa ali protoni, obsevajo vezje ali preidejo skozi integrirano vezje. Posledica tega je motnja v sistemski logiki.

Moteče je tudi “lepljenje” enega dogodka (angl. Single Event Latch-Up, SEL). To je stanje, ki povzroči izgubo funkcionalnosti naprave zaradi visokega induciranega toka, ki ga lahko povzroči en dogodek. SEL je lahko uničujoč ali pa tudi ne. V primeru destruktivnega “lepljenja” se tok ne bo povrnil na nazivno vrednost. V primeru nedestruktivnega “lepljenja” se bo visokonivojski tok vrnil na nazivno vrednost po ponovnem vklopu FPGA.

Primerjava FPGA tehnologij

Obstajajo štiri osnovne vrste FPGA-jev.

FPGA-ji na osnovi SRAM

FPGA, ki temelji na SRAM, shranjuje konfiguracijske podatke logičnih celic v statični pomnilnik. SRAM je volatilen – nestanoviten in ne more ohraniti konfiguracije naprave brez napajanja. Zato je treba FPGA programirati ob vklopu. Tehnologija, ki temelji na SRAM, pri delovanju običajno porabi več energije in je bolj občutljiva na sevanje.

FPGA-ji na osnovi Flash pomnilnika

FPGA, ki temelji na Flash pomnilniku, je mogoče ponovno programirati, saj uporablja Flash pomnilnik kot primarni vir za konfiguracijski pomnilnik. Flash tehnologija je imuna na SEU, kar odpravlja nevarnost motenj, ki jih povzroča sevanje, v konfiguracijskem FPGA pomnilniku. RTG4 FPGA-ji na osnovi Flash pomnilnika porabijo do 50 odstotkov manj energije v primerjavi z FPGA-ji, ki temeljijo na SRAM.

Flash tehnologija poenostavlja načrtovanje na več načinov, saj ni potrebe po zunanjem pomnilniku, redundanci ali neprekinjenem spremljanju konfiguracije. Prav tako odpravlja potrebo po hladilniku, zmanjšuje velikost in težo konstrukcij, hkrati pa zmanjšuje porabo energije, kar je lahko še posebej pomembno, če se elektronski modul napaja s sončnimi paneli.

FPGA-ji na osnovi SONOS pomnilnika

Primer je Microchip RT PolarFire FPGA, ki ponuja odpornost na sevanje z značilnimi podatki o sevanju, nizko močjo, odpornostjo na SEU konfiguracijo in visoko zanesljivimi komponentami s potjo do kvalifikacije QML-V. Ti FPGA so razviti na nevolatilni (NV) tehnologiji silicijev-oksid-nitrid-oksid-silicij (SONOS) na 28nm tehnologiji.

Zmogljivost 28nm in prejšnjih 65nm tehnologij je bila primerjana z merjenjem zakasnitve širjenja signala v pretvorniku. Ti testi kažejo, da 28nm SONOS tehnologija ponuja 2,5-krat večjo zmogljivost kot 65nm Flash tehnologija. FPGA, ki temeljijo na SONOS, imajo tudi izjemno odpornost proti sevanju in proti SEU, hkrati pa ponujajo rešitev z nizko porabo. S potjo do QML-V kvalifikacije so FPGA, ki temeljijo na SONOS, idealni za aplikacije, ki zahtevajo hitro obdelavo signalov.

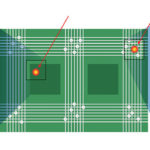

Slika 1 prikazuje, kako so FPGA, ki temeljijo na Flash in SONOS, zasnovani tako, da zagotavljajo odpornost proti SEU.

Antifuse FPGA-ji

FPGA, ki temelji na enkratno programirljivih bitih (angl. fuse bits), se programira enkrat, kar omejuje ključno prednost pri ponovnem programiranju v primerjavi z FPGA, ki temelji na Flash in SONOS. Programirljivi deli FPGApo proizvodnem procesu ne prevajajo toka, ampak jih je potrebno prekiniti (angl. to burn), da prevajajo tok (kar je v nasprotju z običajno varovalko, ki pregori ob previsokem toku). Tehnologija Antifuse je zelo robustna proti učinkom sevanja.

Kako razviti RT FPGA

RT FPGA so razviti na procesnih tehnologijah, ki imajo odlično odpornost na TID sevanja. Lahko so RHBD, s Flip-Flopi, ki imajo vgrajen TMR na nivoju vezja. TMR, nameščen v programski opremi, znan tudi kot mehki TMR, je mogoče implementirati, če TMR še ni bil implementiran na ravni silicija. Ko je silicij razvit, gredo RT FPGA skozi strogo kvalifikacijo.

Da so naprave kvalificirane po najvišjem standardu, se morajo držati MIL-PRF-38535 standarda, ki ga je izdalo ministrstvo za obrambo, ki je tudi ustvarilo dosledne standarde kvalifikacij, testiranja in zanesljivosti za vojaške in vesoljske IC. MIL-PRF-38535 opredeljuje zahteve za proizvajalce IC-jev, če želijo biti navedeni na QML s strani Defense Logistics Agency (DLA).

Drug vidik razvoja izdelka je značilnost SEE delovanja, ki se ne spreminja od serije rezin do serije rezin, če je zasnova silicija enaka. Po dokončanju zasnove lahko proizvajalci FPGA začnejo postopek SEE karakterizacije. Ko je naprava v proizvodnji, ni potrebno dodatno testiranje na SEE delovanje, dokler ni bilo sprememb v zasnovi in je komponenta v celoti označena.

Nekatere procesne tehnologije imajo lahko TID zmogljivost, ki se razlikuje glede na rezine od serije do serije. Posledično je treba testiranje TID zmogljivosti opraviti v proizvodnji na podlagi serije rezin, da se zagotovi, da bo naprava izpolnjevala svojo ciljno specifikacijo ravni TID (25 krad, 100 krad, 300 krad).

Vpliv RT FPGA na razvoj vesoljskih plovil

Najnovejši RT FPGA ponujajo številne prednosti, ki ustvarjajo priložnosti za poenostavitev teh načrtov, hkrati pa znatno izboljšajo zmogljivost za vgrajeno obdelavo podatkov. Da bi izpolnili te potrebe, se vozlišča RT FPGA tehnologije krčijo, da bi ponudila večjo zmogljivost in hitrejšo obdelavo signalov z večjim pomnilnikom in boljšimiDSP zmogljivostmi.

RT FPGA ponujajo tudi druge ključne prednosti, vključno s ponovnim programiranjem in hitrejšim razvojnim časom v primerjavi z ASIC. Običajno se FPGA ne programirajo ponovno, ko so v vesolju, vendar je tudi to možnost, ko se načrti zapletejo, ob predpostavki, da razvojniki sistemov sledijo smernicam in natančno ocenijo stopnjo uspešnosti in tveganja, povezana s ponovnim programiranjem na orbiti.

Opomba: Ime in logotip Microchip sta registrirani blagovni znamki podjetja Microchip Technology Incorporated v ZDA in drugih državah. Vse druge blagovne znamke, ki so morda tu omenjene, so last njihovih podjetij.

https://www.microchip.com