S prelaganjem nalog in dejanj iz primarnega mikrokontrolerja ali mikroprocesorja na mikrokontrolerje, ki so primerni za specifično nalogo, boste poenostavili proces načrtovanja za različne aplikacije.

Microchip Technology Inc.

Avtor: Robert Perkel

V današnjem svetu so vse pogostejši veliki 32-bitni mikrokontrolerji (MCU) in mikroprocesorji (MPU), ki izvajajo operacijski sistem v realnem času (RTOS). Vendar pa lahko en sam velik mikrokontroler, ki obdeluje kompleksno aplikacijo, naleti na težave s CPE viri v zvezi z majhnimi gospodinjskimi opravili, ki niso zapletena, vendar zahtevajo veliko časa.

Manjše mikrokontrolerje, kot so 8- in 16-bitni MCU-ji, je mogoče uporabiti za razbremenitev teh nalog, ki bi jih opravil 32-bitni mikrokontroler. To dejstvo poganja inovacije in razvoj v celotnem spektru mikrokontrolerjev vse od 8-bitnih do 32-bitnih.

Številne naloge so bolj obvladljive, če 32-bitni MCU nekatere od teh nalog prenese na podprocesorje, ki obravnavajo samo 1 ali 2 od teh nalog, vendar pri tem potrebujejo malo nadzora. To sprosti CPE vire na glavnem procesorju, kar zmanjša kompleksnost programske opreme, hkrati pa izboljša zmogljivost in čas izvajanja.

Na primer, 8-bitni MCU se lahko uporabi za ustvarjanje V/I ekspanderja. V/I ekspanderji niso zapletene naprave, vendar zaradi pogostega servisiranja prekinitev porabijo veliko CPE časa. Z uporabo namenskega MCU za to nalogo lahko večja naprava zmanjša izkoriščenost V/I in število prekinitev, ki jih mora obravnavati. Poleg tega je nabor funkcij V/I ekspanderja nastavljen v programski opremi, kar omogoča, da ga prilagodite aplikaciji.

Največja prednost ustvarjanja V/I ekspanderja, z uporabo 8-bitnega MCU, je prilagodljivost. Nabor funkcij ASIC V/I ekspanderja je določen z vezjem znotraj ASIC čipa, medtem ko MCU definira svoje delovanje na podlagi programske opreme, ki jo izvaja. Ta prilagodljivost omogoča, da se različica, ki temelji na MCU, prilagodi potrebam končne aplikacije.

Uporaba naprednega I/O ekspanderja

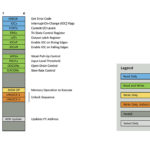

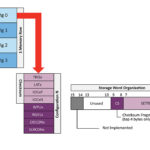

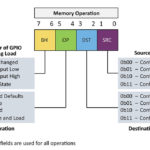

Napredni V/I ekspander interno deluje na podlagi strukture, ki temelji na iskalni tabeli. Pred branjem ali pisanjem se pošlje virtualni naslov. Ta naslov ni v korelaciji z registri na mikrokontrolerju – specifičen je samo za iskano tabelo.

To pomeni, da je mogoče pregledno dodajati funkcije, ki niso v registrih strojne opreme mikrokontrolerja. Vnose v tabeli je mogoče enostavno preurediti tudi za posebne namene. Druga prednost te strukture je možnost dodajanja dovoljenj v iskalno tabelo. Če želite na primer ustvariti register samo za branje, preprosto izpustite vnos v iskalno tabelo za pisanje.

Ta kompleksnejša struktura je primerna tudi za nestandardne funkcionalnosti. Funkcija “MEM OP” MCU -ju omogoča to, da shrani ali naloži svojo trenutno konfiguracijo vhoda in izhoda splošnega namena (GPIO) v pomnilnik.

MEM OP lahko tudi ponastavi konfiguracijo GPIO na parametre, nastavljene pri prevajanju.

Po želji lahko mikrokontroler nastavite tako, da ob vklopu naloži shranjene nastavitve. Če je to omogočeno, mikrokontroler poskuša naložiti nastavitve v konfiguraciji 0. Če konfiguracija ne uspe preveriti kontrolne vsote, se bo MCU vrnil na časovne konstante prevajanja. To funkcijo je mogoče onemogočiti v programski opremi, če tega ne želite.

Prednost rešitve, ki temelji na MCU, je v izjemni meri prilagodljivosti. Za razliko od ASIC-ov na trgu je mogoče MCU konfigurirati z nestandardnimi funkcionalnostmi, značilnimi za aplikacijo, ki se uporablja. Ta aplikacija je bila razvita za družino MCU-jev splošnega namena PIC16F15244. Izvorna koda je na voljo na Microchip Discover (discover.microchip.com) in Github-u.

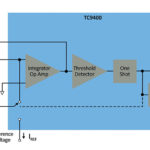

Pretvornik napetosti v frekvenco (V/F)

Pretvornik napetosti v frekvenco (V/F) prikazuje uporabo perifernih naprav strojne opreme za ustvarjanje funkcije, ki je neodvisna od jedra, ki bi jo običajno morali ustvariti z zunanjim integriranim vezjem. Ena največjih prednosti te konfiguracije je, da so zunanje naprave nastavljene v programski opremi, kar olajša spreminjanje primera. Druga prednost je, da je pretvornik implementiran v mikrokontroler, kar zmanjša seznam komponent (BOM) in potrebno površino za načrtovanje.

Eden od izzivov pri pristopu, ki temelji na MCU, je, da ne deluje tako dobro kot analogna rešitev, saj je ločljivost izhoda sama po sebi omejena z ADCC. Nominalno je ADCC 12-bitni, vendar je bil konfiguriran za prevzorčeno 14-bitno ločljivost. Podobno ima vgrajeni numerično krmiljen oscilator (NCO), ki sintetizira izhodno frekvenco, končno ločljivost in ima lahko tresenje na izhodu, odvisno od vrednosti, ki jo izmeri ADC.

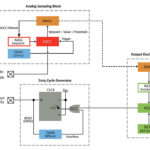

Za izvedbo te rešitve obstajajo trije različni bloki perifernih naprav – analogni blok za vzorčenje, blok izhodnega oscilatorja in generator delovnega cikla.

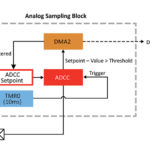

Blok analognega vzorčenja

Za analogno-digitalno pretvorbo je odgovoren blok analognega vzorčenja. Da je mogoč 100 kHz izhod s frekvenčnimi mejami naprave, je bil ADCC konfiguriran tako, da zbira več vzorcev in nato povpreči, da dobi 14-bitni rezultat prevzorčenja.

Slaba stran tega prevzorčenja je dodaten statistični šum, dodan rezultatu. Šum se kompenzira s povprečjem prevzorčenja in dodajanjem histereze. Za izvedbo histereze se uporablja funkcija prekinitve praga ADCC. Za preprostost bodo zajete le podrobnosti o tem, kako ta primer uporablja funkcijo prekinitve praga.

Ko ADCC konča z izračunom povprečnega prevzorca, se dobljena vrednost primerja z registrom nastavljene vrednosti na periferni napravi. Če je razlika med obema večja ali manjša od nastavljenih pragov, se sproži prekinitev. CPE prikrije to prekinitev in nanjo ne vpliva, vendar ta prekinitev sproži kopijo povprečnega rezultata prevzorčenja v registru nastavljene vrednosti ADCC, ki posodobi srednjo točko histereze. Če pragovi niso preseženi, se ta DMA kopija ne bo zgodila, kar ne bo sprožilo posodobitve DMA izhodnega oscilatorskega bloka.

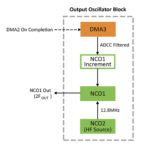

Blok izhodnega oscilatorja

Blok izhodnega oscilatorja te rešitve je odgovoren za generiranje taktnega signala na želeni izhodni frekvenci. Ta izhodni signal je interno povezan z generatorjem delovnega cikla, ki prepolovi frekvenco signala, vendar ustvari 50-odstotni izhod delovnega cikla. Zaradi tega blok izhodnega oscilatorja deluje na dvakratni frekvenci izhodne frekvence.

Srce bloka izhodnega oscilatorja je numerično krmiljen oscilator (NCO). Periferna enota NCO deluje tako, da doda vrednost prirastka akumulatorju na naraščajočem robu vhodne ure. Prelivanje akumulatorja se uporablja za pridobivanje izhoda periferne naprave. Za popolno razlago o delovanju NCO si oglejte podatkovni list.

V tem primeru je bil NCO2 nastavljen tako, da interno ustvari zahtevano vhodno frekvenco ure, da dobi izhod 100 kHz iz 14-bitnega vhoda. 14-bitni rezultat se uporablja, ker izvorni 12-bitni rezultat ADCC ni dovolj velik, da bi ustvaril 100 kHz izhod brez zunanjega vira takta.

| ADC Rezultat | NCO1 izhod (dvojni) | Izhodna frekvenca |

| 0x0000 | 0 Hz | 0 Hz |

| 0x0001 | 12.2 Hz | 6.1 Hz |

| 0x0100 | 3.1 kHz | 1.6 kHz |

| 0x1000 | 50 kHz | 25 kHz |

| 0x3FFF | 200 kHz | 100 kHz |

Če se izhodna frekvenca NCO2 spremeni ali se uporabi alternativni vir takta, bo izhodna frekvenca prilagojena na drugo izhodno območje. Na primer, če se NCO2 zmanjša na 1,28 MHz, izhod doseže največ 10 kHz.

| ADC Rezultat | NCO1 izhodna frekvenca (dvojna) | Izhodna frekvenca |

| 0x0000 | 0 Hz | 0 Hz |

| 0x0001 | 1.2 Hz | 0.6 Hz |

| 0x0100 | 312.5 Hz | 156.3 Hz |

| 0x1000 | 5 kHz | 2.5 kHz |

| 0x3FFF | 20 kHz | 10 kHz |

Idealni izhodi 10kHz V/F pretvornika, z izklopljenim Watchdog-om.

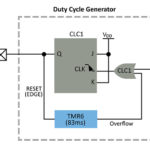

Generator delovnega cikla

Blok generatorja delovnega cikla te rešitve je odgovoren za ustvarjanje 50-odstotnega izhoda delovnega cikla. Ta funkcija je neobvezna – izhod NCO se lahko uporablja neposredno, čeprav se delovni cikel razlikuje v veliko večji meri. Ta generator je izveden z uporabo ene od nastavljivih logičnih celic (CLC). CLC-ji so majhni bloki diskretne nastavljive logike, podobni eni celici FPGA (Field Programmable Gate Array). CLC-ji se lahko uporabljajo kot diskretna logična vrata, kot sta IN-ALI ali ALI-XOR. Lahko jih konfigurirate tudi kot zapahe ali flip-flope. V tej rešitvi je bil CLC implementiran kot J-K flip-flop z resetom. J in K ostaneta na logični HIGH. Blok izhodnega oscilatorja se uporablja kot takt za flip-flop. Vsak impulz vhodnega takta povzroči preklop izhoda, kar ustvari 50-odstotni delovni cikel. Opomba: frekvenčno tresenje iz bloka izhodnega oscilatorja bo vplivalo na delovni cikel. Timer 6 se uporablja kot astabilen “watchdog” timer. Če na izhodu ne pride do roba (naraščajočega ali padajočega), se bo timer prelil in ustvaril taktni impulz za CLC. To nadzoruje nizko stran izhodnega frekvenčnega območja. Namesto da bi dosegel DC, se izhod preklopi na polovico frekvence timerja za izhodni signal 6 Hz. Za izvedbo primera je bila izbrana družina MCU-jev PIC18-Q43 zaradi velikega števila zunanjih naprav v uporabi. Izvorna koda za ta projekt je na voljo na Microchip Discover (discover.microchip.com) in Github.

Zaključek

Medtem ko so visoko zmogljivi mikrokontrolerji in mikroprocesorji na trgu prisotni z nizko ceno, so 8 in 16-bitni MCU-ji neprecenljivo orodje za izvajanje majhnih, specializiranih nalog. Naloge ni nujno, da so zapletene, vendar so lahko dolgotrajne ali časovno kritične. Z razbremenitvijo nalog imajo lahko 32-bitne naprave enostavnejše izvedbe, ki izboljšajo zanesljivost, zmanjšajo porabo pomnilnika in manjšo porabo energije.

Opomba: Ime in logotip Microchip sta registrirani blagovni znamki podjetja Microchip Technology Incorporated v ZDA in drugih državah. Vse druge blagovne znamke, ki so morda tu omenjene, so last njihovih podjetij.

https://www.microchip.com