Lansko leto sem napisal serijo člankov za revijo Svet elektronike, kjer sem predstavil novo skupino vezij podjetja Cypress, ki se imenujejo Programmable System on Chip (programabilni sistem na čipu) ali kratko PSoC. Takrat sem uporabil PSoC4 serijo in glede na prejšnje verzije, so te novi čipi vsebovali zmogljiv procesor z jedrom ARM Cortex-M0.

- Vsebovalo je DIP priključke (z 0,1” razmikom) za lažjo montažo na Vector prototipna vezja, ki jih uporabljam.

- Naredili so večino I/O priključkov dosegljivih na teh priključkih in jih rezervirali samo nekaj za krmiljenje periferije na ploščici.

- Vsebuje programator, ki ga lahko odlomimo. Programator lahko enostavno odstranimo, ko je bil razvoj dokončan.

Odkar sem napisal te članke se je pojavila nova verzija CY8CKIT-043 kita (USD $10), ki je boljša izbira, saj vsebuje zmogljivejši procesor PSoC4200M in vsebuje bolj napredno programiranje/razhroščevanje.

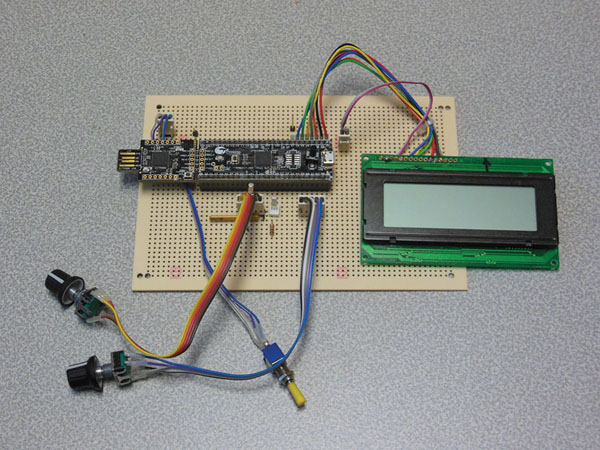

Naredil sem nekaj projektov s PSoC4 vezji, ampak je Cypress relativno hitro predstavil PSoC5LP vezja. Te so precej zmogljivejši, saj uporabljajo ARM Cortex M3 jedro in vsebuje precej več nastavljivih analognih in digitalnih blokov, kot PSoC4 vezja. K sreči se je Cypress odločil, da bo nadaljeval prakso s podobnim razvojnim orodjem za ta novi čip. Trgu so ponudili CY8CKIT-059 (USD $10), ki ga vidite na Fotografiji 8 v članku.

Najprej sem preizkusil Arduino spin-off, Teensy 3.2 ploščo, ki vsebuje zmogljiv Freescale ARM Cortex-M4 procesor in veliko zmogljive periferije, vključujoč timerje, ki bi bili zmožni generirati vse zgoraj naštete funkcije. Precej dobro poznam Arduino IDE (z dodatki, ki omogočajo delo z ostalimi procesorji). Vendar pa, ko sem prebral prvih 60 strani dokumentacije posvečene samo enemu timer modulu v tem MCU-ju in še nekaj Freescale aplikacij (s primeri programov) še vedno nisem bil v stanju, da bi FlexTimer modul bil zmožen izvajati kompleksne, sinhronizirane PWM funkcije, kot omenjeno zgoraj.

Redko kdaj se vdam pri projektu, vendar pa sem se v tem projektu odločil, da dam Teensy3.2 ploščo nazaj na polico in pričel sem znova s Cypress PSoC5LP čipom tako, da bi nov CY8CKIT-059 uporabljal kot osnovo za svoj bodoči projekt.

Lastnosti PSoC5LP

Preden gremo v podrobnosti projekta, bi najprej rad izpostavil nekaj lastnosti PSoC5LP družine. Dejanski PSoC5LP čip, ki se nahaja na razvojni plošči, je čip CY8C5888LTI-LP097. Vsebuje ARM Cortex-M3 procesor z veliko spomina: 256 kB Flash spomina in 64 kB SRAM-a. Ugotovil sem, da bi za ta projekt potreboval precej več Flash pomnilnika, če bom uporabil PSoC5 kot pa bi ga porabil z AVR mikrokontrolerjem, zato je ta veliko količina spomina uporabna. Velika večina tega spomina je uporabljena za hardversko konfiguracijo PSoC programabilnih blokov in internih analogno/digitalnih poti, ki jih povezujejo.

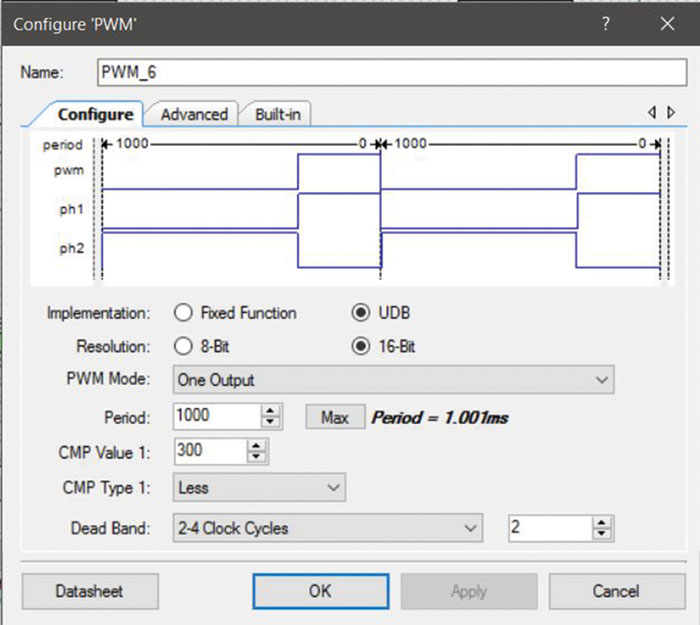

Vezje vsebuje štiri 16-bit Timer module, ki jih lahko uporabimo v več PWM konfiguracijah. Vsebuje tudi 24 UDB-jev (Universal Digital Block – univerzalni digitalni blok). Lahko jih nastavimo na več možnosti, vključujoč več različnih PWM funkcij vključno vse za izbrane funkcije, ki jih uporabljam v projektu.

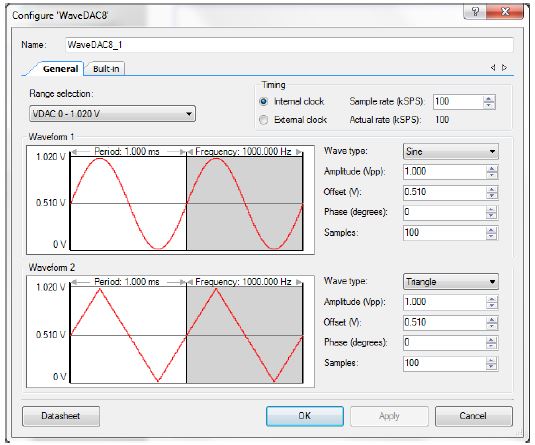

Vezje vsebuje tudi veliko analognih funkcij: 20-bit Sigma-Delta ADC, dva 12-bit SAR ADC, štiri 8-bit DAC in široko izbiro operacijskih ojačevalnikov/komparatorjev. Vsebuje tudi 4 Programabilne Analogne Bloke, ki jih lahko konfiguriramo v ojačevalnik z nastavljivim ojačenjem, mešalnik itd. V tem projektu nisem uporabil veliko od pripadajočih programov razen DAC.

Multi-test: Univerzalni tester na osnovi PSoC5LP modula podjetja Cypress

2016_SE241_27