Po hitri širitvi možnosti uporabe SiC izdelkov je naslednji izziv industrije poenostavitev postopka načrtovanja za končne uporabnike. Razvijalci elektroenergetskih sistemov potrebujejo holistične rešitve, ki ne obravnavajo samo tipičnih elementov oblikovanja posamično, ampak tudi priznavajo pomen njihove interakcije.

Povedano drugače, ambiciozni dobavitelji SiC ne smejo samo pokazati učinkovitosti in robustnosti svoje SiC MOSFET tehnologije, temveč morajo pomagati pri načrtovanju izzivov tako, da ponujajo ohišja z nizko induktivnostjo in bolj dovršene gonilnike za podporo, zaščito in natančno prilagajanje sistemskih parametrov. Natančen razmislek o teh treh ključnih delih bo zagotovo poenostavil presojo in oblikovanje tistih, ki želijo izkoristiti moteče vplive in s tem v zvezi izboljšave na ravni sistema, ki jih omogočajo izdelki SiC tehnologije.

Robustni in togi SiC MOSFET

Kot verjetno najpomembnejši člen v verigi elektroenergetskih sistemov, morajo SiC MOSFET tranzistorji pokazati robustnost na več ključnih področjih, kjer so bili prej tradicionalno ranljivi. Tako kot silicijevi MOSFET-i, se tudi SiC soočajo s problemom zunanjih napak, kot so nečistoče, stanja nabojev in druge materialne napake v bližini meje med oksidom in polprevodnikom, ki povzročajo številne nestabilnosti naprave in mehanizme slabljenja. Odprava teh tveganj zahteva, da imajo SiC MOSFET-i iz redne proizvodnje pri pogojih pod lavinskim efektom stabilno mejno napetost, zanesljiv oksid vrat, robustnost vgrajene lastne zaščitne diode in splošno robustnost. Vsak atribut je treba potrditi s preizkusom usposobljenosti, saj se lahko parametrična stabilnost in življenjska doba od enega do drugega dobavitelja dramatično razlikujeta.

Za preizkušanje stabilnosti praga napetosti (Vth) SiC MOSFET-a je običajna praksa, da pozitivne (p-HTGB) in negativne (n-HTGB) visokotemperaturne odklone napetosti vrat uporabimo na statistično zadostnem številu posameznih komponent in preprosto primerjamo Vth celotne populacije pred in po stresu. Na primer, p- in n-HTGB sta bila izvedena na neodvisnih sklopih štiriinšestdesetih 1200 V SiC MOSFET-ov v 1.000 urah. Povprečna sprememba Vth je bila +59,6 milivoltov po p-HTGB kriteriju in -22,8 milivoltov po n-HTGB kriteriju. Na tej ravni stabilnosti imajo razvijalci predvidljivi mejni napetosti, okoli katerih lahko načrtujejo manj ohlapno in bolj dolgoročno.

Visoko zanesljivi oksidi na vratih so ključnega pomena za vse aplikacije, zlasti tiste, ki zahtevajo dolgo življenjsko dobo. Za določitev zanesljivosti samega SiC MOSFET-ovega oksida so bile opravljene meritve naboja do razgradnje (QBD) na treh populacijah SiC MOSFET-ov 1200 V. Vse opažene okvare so bile prirojene narave, kar kaže na visoko stopnjo zrelosti procesa. Stopnje napake v času (FIT) in povprečni čas do okvare (MTTF) so bile izračunane z uporabo širše populacije 192 komponent. Za p-HTGB je bilo ugotovljeno, da sta ti vrednosti 20 in 5618 let; za n-HTGB je bil FIT 93 s časom MTTF 1233 let. To je dobra spodbuda za končne uporabnike, saj so ti rezultati skladni s poročili o časovno odvisnih dielektričnih razgradnjah (TDDB) več različnih proizvajalcev.

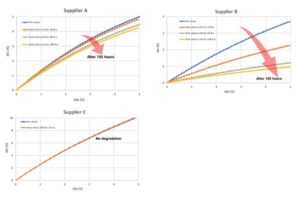

Pojav bipolarne razgradnje na p-n spojih SiC MOSFET tranzistorjev je bil globoko raziskan. Če bi se to zgodilo na zaščitni diodi SiC MOSFET-a, bi bilo to opaziti kot povečanje upornosti v prevodnem stanju in padcu napetosti na diodi med prevajanjem toka (kar je razvidno iz škodljivega premika v izhodnih značilnostih tretjega kvadranta). K sreči je SiC MOSFET tehnologija že toliko dozorela, da se je gostota obstoječih napak v samem kristalu zmanjšala že v fazi proizvodnje. Kljub temu pa je treba ovrednotiti MOSFET-e vsakega proizvajalca. Državna univerza Ohio je pred kratkim raziskala razgradnjo vgrajene zaščitne diode pri 100 urah delovanja s polnim nazivnim tokom (VGS = -5 V) pri 1200 V SiC-MOSFET-ih različnih proizvajalcev, kar je pokazalo velike post-stresne razlike v upornosti v prevodnem stanju. Samo pri proizvajalcu “C” ni bilo opaziti razgradnje (slika 1). Podatki, ki se nahajajo v tretjem kvadrantu na enakih komponentah, potrjujejo prisotnost (ali odsotnost pri dobavitelju “C”) razgradnje vgrajene zaščitne diode.

Drug pomemben parameter za oceno je robustnost v zvezi z lavinskim efektom, ki se je izvajala s prostim induktivnim preklopom (UIS). MOSFET se napaja z napetostjo, medtem ko je v izklopljenem stanju, zaradi česar se ves lavinski tok sproži na obodu substrata, ker MOS kanal ni izboljšan (enhanced). To se seveda razlikuje od preskusa vzdržljivosti ob kratkem stiku, pri katerem je MOSFET v vklopljenem stanju in se tok bolj enakomerno porazdeli po celotnem aktivnem območju komponente. Za natančno posnemanje resničnih pogojev delovanja so SiC MOSFET-i izpostavljeni ponavljajočim se impulzom UIS (R-UIS); parametrična stabilnost in integriteta oksida se primerjata pred in po 100.000 ponavljajočih se impulzih pri dveh tretjinah nazivnega toka (na MIL-STD-750). Na VBR, Vth in VF vgrajene zaščitne diode R-UIS ne vpliva, kar kaže na odlično robustnost v zvezi z lavinskim efektom.

Močnostno ohišje z nizko induktivnostjo

Z zaupanjem v SiC MOSFET je naslednji instrumentalni del celotne SiC sistemske rešitve izbira optimiziranega močnostnega ohišja. Učinkovito modulsko ohišje z več vgrajenimi čipi naj bi oblikovalcem omogočalo izkoristiti prednosti SiC in naj da bi jih pri načrtovanju ne oviralo.

Tu je treba upoštevati številne zahteve. Ker je SiC MOSFET tabletka razmeroma majhna, jih je treba veliko povezati paralelno, da dosežemo nizko upornost v prevodnem stanju. Poleg tega se mora vzporedno vezana matrica MOSFET tranzistorjev preklapljati v enakem času in z enakomerno porazdelitvijo toka, kar pomeni, da mora biti hkrati zagotovljena tako simetrija kot tudi nizka induktivnost v celotni medsebojni shemi povezane matrice.

Dober primer je Microchipovo ohišje SP6LI, ki v napajalno zanko vnaša le 2,9 nanohenrija (nH) stresane induktivnosti v primerjavi z več kot 20 nH parazitske induktivnosti v standardnih modulskih ohišjih. Induktivnost močnostne zanke se zmanjša z razporeditvijo povezav enosmernih tokokrogov na dovodnih zbiralkah. Substratne povezave so simetrično razporejene in nameščene čim bližje polprevodniški matrici. Glede na zanko vrata-vir se za optimizacijo časovnega usklajevanja in enakomerne delitve toka uporabljajo neodvisni serijski upori za vsako od dvanajstih razpoložljivih vej v položajih stikal, ki preklapljajo na visoki in nizki strani. Neodvisni upori na vratih zmanjšajo parazitsko induktivnost, vstavljeno v zanko vrata-vir in ščitijo pred katastrofalnimi prebojnimi dogodki, hkrati pa zmanjšujejo preklopne izgube.

Pametna, prilagodljiva tehnologija gonilnikov vrat

Tretji kritični del, potreben za celotno sistemsko SiC rešitev, je krmiljenje. Še enkrat naj omenimo, da zmožnost hitrega preklopa SiC MOSFET-ov postavlja neoptimiziran sistem v nevarnost velike občutljivosti na motnje zaradi elektromagnetnih interferenc (EMI) in prehodnih napetostnih pojavov. Potreben je povsem nov razred tehnologije krmilnikov vrat, ki omogoča oblikovalcu, da ima možnost manipulacije s preklopno dinamiko in da v aplikaciji doseže optimalne kompromise. Poleg tega mora gonilnik vrat zagotoviti hitro zaznavanje in odziv na prenapetostne pogoje, saj imajo tu SiC MOSFET-i krajši čas vzdržljivosti v primerjavi z večino silicijevih IGBT-jev.

Z uporabo patentirane tehnike, imenovane razširjeno preklapljanje, najnovejše rešitve gonilnikov digitalnih vrat omogočajo zaustavitev z vmesnim nivojem VGS, ki ga določi uporabnik, v želenem trajanju, da izprazni Millerjevo kapacitivnost, preden nadaljuje v VGS za popolno zapiranje (glej sliko 2). To se razlikuje v primerjavi s tradicionalnimi pristopi, ki VGS krmilijo neposredno iz prevodnega v neprevodno stanje, tako da projektantu ne nudijo drugačne poti za izhod iz sistema, s katero bi se bilo mogoče izogniti na primer parazitni induktivnosti kabla, ki se uporablja za priključitev bremena. Vsekakor pa optimalne kompromise med prekoračitvijo napetosti in izkoristkom lahko dosežemo že z rahlimi spremembami v razširjenem preklopnem profilu (nivo VGS in nastavitev časa zadrževanja).

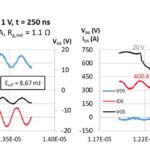

Slika 3 prikazuje izklopne oscilograme z uporabo dveh profilov razširjenega preklapljanja in 1200 V SiC MOSFET modula v ohišju D3 (106 mm x 62 mm x 31 mm). Opazimo lahko, da izbira nižjega nivoja vmesne napetosti VGS zmanjša preklopne izgube, kar je izjemnega pomena v primerih, ko je učinkovitost prednostna naloga. Uporaba višjega nivoja VGS napetosti duši prenapetostne konice na VDS in ublaži nihanja vseh treh valovnih oblik. Z uporabo priloženega orodja za konfiguracijo v obliki programske opreme lahko nastavitve gonilnika vrat natančno nastavite v vseh fazah razvojne poti z miško v roki in klikanjem, kar je gotovo boljši način načrtovanja kot dolge ure, ki bi jih na klasičen način preživeli s spajkalnikom v roki.

Digitalni gonilniki vrat lahko poleg tega nudijo tudi izboljšano inteligenco. Lahko jih na primer uporabimo za proženje povsem drugačnega profila izklopa v primeru okvare, da je s tem zagotovljen varen potek krmiljenja tudi v kritičnih situacijah. Vključitev AS metod v zaščito pred kratkim stikom podkrepljeno z uporabo nizkega Rg krmili mehkejše delovanje MOSFET-a in bolj nadzorovan prehod v izklopljeno stanje z manjšo verjetnostjo pojava lavinskega efekta. Funkcije, ki ponujajo še večjo možnost nastavitev, vključujejo diagnostične meritve v realnem času, kot so napajalna enosmerna napetost in spremljanje temperature.

Ko se oblikovalci močnostne elektronike preusmerjajo s silicijevih IGBT na SiC MOSFET-e, se vedno bolj zanašajo na dobavitelje komponent, ki naj bi zagotavljali opisane ključne elemente, ki so potrebni pri realizaciji celovitih sistemskih rešitev. To vključuje SiC MOSFET z dokazano robustnostjo, močnostno ohišje za ultra nizko induktivnost in nov razred inteligentnih gonilnikov vrat, ki omogočajo lažjo optimizacijo. Vsak od naštetih elementov je predpogoj za nemoteno načrtovanje rešitev s SiC tehnologijo od začetne zasnove do uporabe v dejanskih aplikacijah.

Avtor: Kevin Speer iz podjetja Microchip Technology