Izolirani analogno-digitalni pretvorniki (ADC) s pretvorbo sigma-delta (∑-Δ) so postali najbolj priljubljen način merjenja faznega toka v visokozmogljivih motorjih in servopogonih. Ti pretvorniki zasluženo slovijo po robustni galvanski izolaciji in odlični zmogljivosti merjenja. Z vsako novo generacijo se zmogljivost še poveča, vendar pa lahko potencial najnovejših AD-pretvornikov v celoti izkoristite le z ustreznim načrtovanjem preostalega pogona motorja.

Ta članek je prvi iz serije dveh. Prvi del obravnava demodulacijo sigma-delta kodiranih podatkov s filtri sinc v aplikaciji za krmiljenje motorja. Nato bomo podrobneje obravnavali različne pristope za izvedbo filtrov sinc in sinhronizacijo krmilnega algoritma. Drugi del predstavlja novo strukturo filtra sinc, ki izboljša zmogljivost merjenja v aplikacijah za krmiljenje motorjev. Sledi še razprava o izvedbi filtrov sinc s kodo HDL za optimalno zmogljivost, na koncu pa bomo predstavili rezultate merjenja v 3-faznem servopogonu na osnovi FPGA.

Uvod

Proizvajalci motornih pogonov stalno izboljšujejo zmogljivost in robustnost svojih izdelkov. Določene prednosti so realizirali z naprednejšimi krmilnimi algoritmi in večjo računsko močjo. Druge izboljšave so bile dosežene z zmanjšanjem neidealnih učinkov v tokokrogih za povratne informacije, kot so zakasnitve, časovni zamiki in temperaturno lezenje.1.

Pri povratnih informacijah za krmilni algoritem motorja je najbolj kritični del merjenje faznega toka. S povečevanjem zmogljivosti krmiljenja postane sistem vedno bolj občutljiv na neidealne učinke, kot sotočnost časovne uskladitve, napake odmika/ojačenja in napake pri sinhronizaciji več kanalov za povratne informacije. Skozi leta so se polprevodniška podjetja osredotočila na zmanjšanje teh neidealnih učinkov v verigi signalov za povratne informacije in ta trend se bo verjetno še nadaljeval. ADuM7701 je primer najnovejše generacije izoliranih sigma-delta AD-pretvornikov, optimiziranih za merjenje faznega toka. Zmogljivost AD-pretvornika je pomembna, vendar pa je prisotno tudi veliko tveganje uvajanja neidealnih učinkov v preostali poti za povratne informacije. Ta članek gre mimo samega ADC in govori predvsem o preostalem delu poti povratne informacije. Glavni poudarek je sicer na aplikacijah za krmiljenje motorjev, vendar pa ta članek velja za kateri koli sistem, ki zahteva strogo sinhronizacijo AD-pretvornikov sigma-delta.

Tipično verigo signalov pri uporabi AD-pretvornika sigma-delta kaže slika 1. Analogna vhodna napetost se pridobi na souporu, skozi katerega teče fazni tok. AD-pretvornik sigma-delta pretvori analogni signal v 1-bitni podatkovni tok in zagotavlja galvansko izolacijo, tako da je vse za AD-pretvornikom ločeno od potenciala faze motorja. Pretvorniku sledi demodulacija v obliki filtra. Filter pretvarja 1-bitni signal v večbitnega (M-bitov) in zmanjša hitrost osveževanja s postopkom decimacije. Decimacija v filtru sicer zmanjša hitrost osveževanja podatkov, vendar pa je običajno še vedno prevelika za hitrost osveževanja krmilnega algoritma. To težavo rešimo z dodatno končno stopnjo prevzorčenja.

V tem članku privzemamo, da sta filter in decimacijska stopnja izvedena v napravi FPGA ter da uporabljamo filter sinc tretjega reda (sinc3).

Sinhronizacija filtra sinc

Pogosta kritika pri AD-pretvornikih sigma-delta in filtre sinc je, da jih je težko obvladovati v časovni domeni ter da nimajo točno določenega trenutnega vzorčenja.2. V primerjavi s klasičnim ADC z namenskim vezjem za vzorčenje in zadrževanje imamo v resnici nekaj razlogov za zaskrbljenost. Vendar pa imamo za to tudi rešitve. Kot bomo pokazali v tem razdelku, je ključno, da filter sinc sinhroniziramo s preostalim sistemom in da fazni tok vzorčimo v pravem trenutku. Če tega ne storimo pravilno, bo končna izmerjena vrednost bistveno popačena.

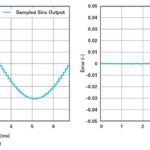

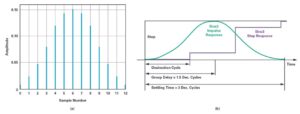

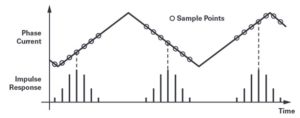

Izhod iz filtra sinc ne predstavlja vhoda v AD-pretvornik sigma-delta v tem trenutku. V resnici je rezultat uteženo povprečje stanja vhoda v določenem preteklem časovnem oknu. To se dogaja zaradi impulznega odziva filtra. Slika 2a kaže impulzni odziv filtra sinc3 za stopnjo decimacije 5. Slika kaže, kako je izhodna vrednost filtra utežena vsota vhodnega zaporedja, ki daje večjo težo vzorcem v sredini in manjšo težo vzorcem na začetku ter koncu.

Pred nadaljevanjem potrebujemo nekaj osnovnih opredelitev. Ura AD-pretvornika sigma-delta, pravimo ji tudi ura modulatorja, imenujemo fmod. Stopnja decimacije (DR) določa frekvenco decimacije (fdec) in je povezana s fmod, kot kaže enačba 1:

Desna stran slike 2 kaže učinek impulznega odziva na stopnični odziv filtra. Ko priključimo stopnico, se izhod filtra ne spremeni takoj, prehodni pojav filtra traja cele tri decimacijske cikle. Na tej podlagi lahko navedemo nekaj pomembnih lastnosti filtra sinc3.

- Zakasnitev skupine znaša 1,5 decimacijskega cikla.

- Umirjanje traja 3 decimacijske cikle.

Te lastnosti so pomembne pri sinhronizaciji filtra s krmilnim sistemom in bodo uporabljene v celotnem članku.

Pred obravnavo sinhronizacije filtra sinc morate določiti značilnosti vhodnega signala. S tem lahko nato določimo, s čim je treba sinhronizirati filter.

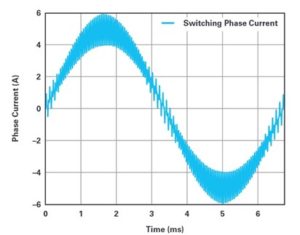

Slika 3 kaže simulirani fazni tok 3-faznega motorja s trajnim magnetom, ki ga poganja razsmernik z napetostnim virom. Modulacijska shema je PWM3 s prostorskim vektorjem, frekvenca preklapljanja pa je 10 kHz. Motor je obremenjen z vršnim faznim tokom 5 A in se vrti s 3000 vrt/min. Ta postavitev pri treh parih polov pomeni temeljno električno periodo 6,67 ms.

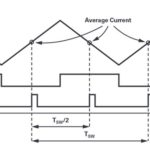

Fazni tok lahko gledamo kot sestavljen iz dveh komponent: povprečja in stikalne komponente. Za krmiljenje je zanimiva le povprečna komponenta toka, zato je treba stikalno komponento v celoti odstraniti. Povprečno komponento najpogosteje izločimo tako, da signal vzorčimo sinhrono z valovno obliko PWM, ki se dovaja na sponke motorja. To kaže slika 4. Zgornji signal kaže stikalno valovno obliko faznega toka, srednji signal kaže signal PWM na visoki strani za ustrezno fazo pretvornika, spodnji pa je sinhronizacijski signal iz časovnika PWM. Sinhronizacijski signal PWM se sproži na začetku in na sredini cikla PWM. Poenostavimo s predpostavko, da vse tri faze delujejo z razmerjem vklopa 50 %, kar pomeni, da ima tok samo eno naraščanje in en padec. Na naraščajočem robu sinhronizacijskega signala PWM ima tok povprečno vrednost, tako da lahko stikalno komponento popolnoma izločimo z vzorčenjem v tem trenutku. Vezje za vzorčenje in zadrževanje je efektivno enakovredno filtru z neskončnim slabljenjem pri stikalni frekvenci.

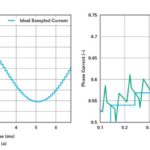

Slika 5 kaže rezultat pri uporabi takšnega vzorčenja na valovni obliki na sliki 3. Na desni strani je prikazan povečan del dejanskega faznega toka in vzorčenega toka. Vidimo, kako postopek vzorčenja in zadrževanja popolnoma odstrani valovitost.

Uporabljena je predstavitev vzorčenega toka na enoto, tako da je vrednost 0 A preslikana na 0,5 in pomeni maksimalni odklon 8 A. To merilo je uporabljeno za lažjo primerjavo z naslednjimi meritvami sigma-delta. Slika 5 kaže idealen scenarij, kjer ostane po vzorčenju samo osnovna komponenta. Ti podatki so zato lahko referenca za primerjavo z meritvami sigma-delta.

Meritve sigma-delta in zrcaljenje

Pri ADC z idealnim vzorčenjem in zadrževanjem lahko izločimo osnovno komponento zaradi natančne določitve trenutka vzorčenja. Pretvorba sigma-delta pa je stalen postopek vzorčenja in je zato valovitost neizogibno del meritve.

Pri pretvorbi sigma-delta imamo tesno povezavo med stopnjo decimacije in razmerjem signal-šum (SNR). Višja stopnja decimacije pomeni večje efektivno število bitov (ENOB) na izhodu. Slaba stran je, da se s povečanjem stopnje decimacije poveča tudi skupinska zakasnitev, zato mora načrtovalec določiti kompromis med ločljivostjo signala in zakasnitvijo v verigi povratne informacije. Na splošno velja, da mora biti zakasnitev majhna glede na periodo krmilnega cikla. Za krmiljenje motorjev so tipične stopnje decimacije od 128 do 256, kar zagotavlja dober kompromis med SNR in skupinsko zakasnitvijo.

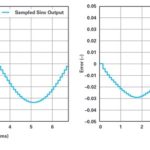

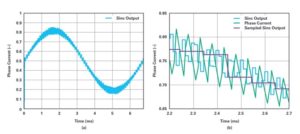

Pri specifikacijah v podatkovnih listih se pogosto uporablja stopnja decimacije 256. ADuM7701 ima na primer vrednost ENOB 14 bitov pri stopnji decimacije256. Pri tako visokem številu ENOB lahko pričakujemo zelo čisto meritev. To lahko preverimo tako, da privzamemo, da je bil fazni tok, prikazan na sliki 3, izmerjen s sigma-delta ADC, ki deluje z uro 20 MHz, in da je podatkovni tok demoduliran s filtrom sinc3 ter stopnjo decimacije 256. Rezultat kaže slika 6a.

Osnovna komponenta faznega toka je očitna, vendar pa ima izmerjeni signal v primerjavi z idealnim vzorčenjem na sliki 5a veliko šuma. ADC in filter sinc tako sicer zagotavljata osupljive številke ENOB, vendar pa je kakovost signala povratne informacije slaba. Razlog za to vidimo na sliki 6b, kjer sta podrobno prikazana izhod filtra sinc in dejanski fazni tok. Vidimo, da je stikalna komponenta faznega toka pri 10 kHz sicer fazno zamaknjena, vendar je filter sinc skorajda ne slabi. Zdaj pa predpostavimo, da se algoritem krmiljenja motorja izvede enkrat na periodo PWM in da se najnovejši izhod filtra sinc odčita na začetku periode. To efektivno pomeni prevzorčenje izhoda filtra sinc, da je usklajen s hitrostjo posodabljanja krmilnega algoritma. Prevzorčenje in tako pridobljen signal kaže vzorčeni izhod filtra sinc na sliki 6b. Slika 7a kaže rezultat za celotno osnovno periodo, ki se filtrira in vzorči s frekvenco PWM.

Jasno je, da je meritev faznega toka močno popačena in bi povzročila slabo zmogljivost krmiljenja. Pričakujemo lahko večjo valovitost navora in potrebo po zmanjšanju pasovne širine tokovne krmilne zanke. Če meritev na sliki 7a odštejemo od idealne (slika 5a), dobimo napako (glejte sliko 7b). Napaka znaša približno 7 % celega signala, kar je bistveno slabše od pričakovanih 14 ENOB.

Ta scenarij merjenja sigma-delta z zrcaljenjem kaže zelo pogost način delovanja merjenja toka po postopku sigma-delta, ki je načrtovalce pripeljal do zaključka, da AD-pretvorniki sigma-delta niso primerni za motorne pogone. Vendar pa ta primer ne kaže na slabo delovanje samega AD-pretvornika. Namesto tega kaže slabo delovanje preostanka signalne verige, saj ni pravilno pripravljena za merjenje faznega toka.

ADC vzorči vhodni signal pri več megahercih (tipično od 10 do 20 MHz), filter sinc pa s stopnjo decimacije 256 učinkovito odpravlja šum zaradi modulacije. Pri tako visoki frekvenci vzorčenja je valovita komponenta faznega toka prisotna v izhodu filtra, kar lahko postane težava v fazi prevzorčenja v signalni verigi (glejte sliko 1). Če valovita komponenta ni primerno zadušena in krmilni algoritem motorja povratno informacijo o toku jemlje s frekvenco PWM, prihaja do zrcaljenja zaradi prevzorčenja.

Zrcaljenje preprečimo, če v signalu ni energije nad polovico frekvence vzorčenja, kot nam pove osnovna teorija vzorčenja. Če izhod ADC sigma-delta prevzorčimo na 10 kHz, na našo meritev vpliva zrcaljenje kakršnega koli šuma s frekvenco nad 5 kHz. Kot smo že pokazali, je bilo v signalu za filtrom sinc prisotnega veliko šuma zaradi preklapljanja pri 10 kHz. Ena od možnosti za slabljenje šuma pri 10 kHz je povečanje stopnje decimacije, vendar pa bi to povzročilo nesprejemljivo veliko skupinsko zakasnitev. Potrebujemo drugačen pristop.

Izboljšanje merjenja s sinhronizacijo

Glavna težava s pristopom do odpravljanja zrcaljenja, ki smo ga uporabili v prejšnjem razdelku, je prikazana na sliki 8. Izhod iz filtra sinc se odčita v trenutku, ki ni povezan s stikalno komponento faznega toka. Ob odčitavanju izhoda nam filter kot rezultat pokaže uteženo povprečje vhodnega signala glede na impulzni odziv. To uteženo povprečje se včasih pridobi na nizkem delu preklopne valovne oblike, včasih pa na visokem. To pomeni, da signal, ki ga uporabimo kot povratno informacijo, vsebuje močan šum pri frekvencah od 0 Hz do polovične frekvence PWM.

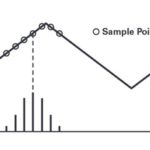

ADC sigma-delta vzorči neprekinjeno, filter sinc pa nam daje več meritev na cikel PWM (tipično od 10 do 20). Ker vsaka meritev obsega tri cikle decimacije, se impulzni odzivi prekrivajo. Za poenostavitev smo na sliki 8 prikazali samo tri od teh meritev in impulznih odzivov.

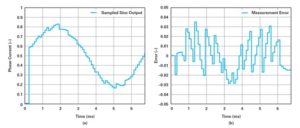

Vir težav je v tem, da impulzni odziv ni povezan s stikalno komponento toka, ki je fiksno povezana s frekvenco PWM. Rešitev je, da stopnjo decimacije izberemo tako, da se v vsaki periodi PWM opravi fiksno celo število decimacijskih ciklov. Pri frekvenci PWM 10 kHz, uri modulatorja 20 MHz in stopnji decimacije 200 imamo točno 10 ciklov decimacije na periodo PWM. Pri fiksnem številu ciklov decimacije na periodo PWM je impulzni odziv ves čas fiksno povezan s PWM in se meritev za povratno informacijo vedno zajame na isti točki znotraj cikla PWM. Na sliki 9a je prikazana meritev faznega toka pri taki shemi sinhronizacije.

Očitno je, da smo s sinhronizacijo impulznega odziva s PWM dosegli pozitiven učinek. Šum je odpravljen in meritev je na prvi pogled videti podobna idealni na sliki 5a. Ko pa meritev sigma-delta odštejemo od idealne meritve, je rezultat signal napake na sliki 9b. Velikost napake je podobna kot na sliki 7b, spremenil pa se je frekvenčni spekter. Zdaj je napaka harmonik prvega reda, ki je enak napaki ojačenja. Razlog za ta vzorec napake kaže slika 10.

Komponenta napake z belim šumom je odpravljena, vendar pa je signal še vedno popačen, ker stikalna komponenta enostransko vpliva na meritev. Na sliki 10 lahko vidite, kako daje impulzni odziv filtra sinc uteženo povprečje okoli konice preklopne valovne oblike. Odvisno od faze impulznega odziva glede na PWM je velikost tega vpliva omejena samo z velikostjo valovitosti toka. Kot kaže slika 3, se velikost valovite komponente spreminja po eni osnovni periodi: največja je pri vršni vrednosti osnovnega toka in najmanjša pri prečkanju skozi ničlo. Zaradi tega je merilna napaka harmonska komponenta prvega reda.

Merilne napake zaradi harmonske komponente prvega reda se lahko znebimo, če je impulzni odziv vedno postavljen na sredino okoli začetka ali sredine periode PWM, ko je fazni tok točno na vrednosti povprečja. Slika 11 kaže impulzni odziv s sredino na začetku obdobja preklopa. Okoli te točke je preklopna valovna oblika simetrična, tako da imamo enako število izmerjenih točk na vsaki strani in se valovita komponenta okoli te točke povpreči na ničlo.

Ko je impulzni odziv fiksno povezan s periodo preklapljanja in poravnan s točko povprečnega toka, je rezultat meritve prikazan na sliki 12a, napaka meritve pa na sliki 12b. Enako kot meritev z idealnim vzorčenjem ta signal nima belega šuma in napake ojačenja.

Prikazani rezultati kažejo, da je kakovost meritve sigma-delta odvisna od veliko več kot le stopnje decimacije. Pogosto prepričanje, da lahko s povečanjem stopnje decimacije dosežemo višje število ENOB, drži le, ko ne prihaja do zrcaljenja. Uravnavanje frekvence posodabljanja filtra in faze glede na vhodni signal je bistveno pomembnejše od stopnje decimacije. Za primer vzemimo sliko 7, ki je temeljila na stopnji decimacije 256, in sliko 12, ki je temeljila na stopnji decimacije 200. Nižja stopnja decimacije je bistveno izboljšala meritev.

Povzetek 1. dela

Če povzamemo, so pogoji za optimalno merjenje faznega toka z AD-pretvornikom sigma-delta naslednji:

- Impulzni odziv filtra sinc tretjega reda traja tri cikle decimacije, kar pomeni, da traja prehod podatkov skozi filter tri cikle decimacije.

- Impulzni odziv filtra mora biti poravnan s središčem na trenutku povprečnega toka.

- 1,5 decimacijskega cikla impulznega odziva mora ležati pred trenutkom povprečnega toka, 1,5 decimacijskega cikla pa po njem.

- V eni periodi PWM da filter sinc več izhodnih vrednosti, vendar uporabimo le eno. Ostale zanemarimo.

S tem končujemo 1. članek v tej seriji. V 2. delu bomo predlagali novo strukturo filtra sinc, ki je posebno primerna za krmiljenje motorjev, in se pogovorili o najboljšem možnem načinu izvedbe filtrov sinc z napravami FPGA. Za potrditev idej, o katerih smo se pogovarjali v tej seriji člankov, imamo v 2. delu tudi predstavitev več meritev, opravljenih na 3-faznem servopogonu, ki temelji na napravi FPGA.

Reference

1 Jens Sorensen and Dara O’Sullivan.“A System Approach to Understandingthe Impact of Nonideal Effects in a Motor Drive Current Loop.” Proceedings of PCIM Europe 2016.

2 Jens Sorensen. “∑-Δ Conversion Used for Motor Control.” Proceedings of PCIM Europe 2015.

3 Ahmet M. Hava, Russel J. Kerkman, and Thomas A. Lipo. “SimpleAnalytical and Graphical Methods for Carrier-Based PWM-VSI Drives.” IEEE Transactions on Power Electronics, January 1999.

O avtorju

Jens Sorensen je inženir za sistemske aplikacije pri podjetju Analog Devices, kjer dela na rešitvah za krmiljenje motorjev za industrijsko uporabo. Ima diplomo M.Eng.Sc. iz Univerze Aalborg na Danskem. Zanimajo ga predvsem krmilni algoritmi, močnostna elektronika in krmilni procesorji. Dosegljiv je na naslovu jens.sorensen@analog.com.

O avtorju

Dara O’Sullivan je inženir za sistemske aplikacije v ekipi za povezano premikanje in robotiko v poslovni enoti za avtomatizacijo ter energetiko pri podjetju Analog Devices. Njegovo strokovno področje so pretvarjanje moči, krmiljenje in nadzor v industrijskih aplikacijah za krmiljenje gibanja. Ima diplomo B.E, M.Eng.Sc. in Ph.D. iz univerze University College Cork na Irskem, od leta 2001 pa je delal na številnih aplikacijah za industrijo in obnovljive vire energije na številnih delovnih mestih za raziskave, svetovanje ter industrijo. Dosegljiv je na naslovu dara.osullivan@analog.com.

O avtorju

Shane O’Meara je inženir za sistemske aplikacije v ekipi za povezano premikanje in robotiko pri podjetju Analog Devices. Njegovo strokovno področje so natančno pretvarjanje in signalne verige za krmiljenje in nadzor v industrijskih aplikacijah za krmiljenje gibanja. Ima diplomo B.Eng. iz Univerze Limerick, v podjetju Analog Devices pa dela od leta 2011. Dosegljiv je na naslovu shane.omeara@analog.com.

Avtorji: Jens Sorensen, Dara O’Sullivan in Shane O’Meara